#### CHAPTER FOUR

## Register Transfer and Microoperations

### IN THIS CHAPTER

| Middle a Loobs of Reinsyno over           | 4-1 | Register Transfer Language |

|-------------------------------------------|-----|----------------------------|

| di bas eraseigni divavitad el l'ambili la | 4-2 | Register Transfer          |

| of grateria and draw bear capaes after to | 4-3 | Bus and Memory Transfers   |

- bas basinsano as solawarq at lisagithe ovitaro Arithmetic Microoperations 4-4

- Logic Microoperations 4-5 Shift Microoperations 4-6

- Arithmetic Logic Shift Unit 4-7

### 4-1 Register Transfer Language

a sureties nevertarit erispirio pirculeris warmed for vinicialitays. Inthe advice in the same

stated midropperaiten and transfer the pestit of the operation to the same or

why examinateory most betrartied, at longuages! brow pall, consists teritoris

of box models so in applications audions qui

and desired the transpopulation and the contraditions

statement" restrat set I laga unitral violentical to

A digital system is an interconnection of digital hardware modules that accomplish a specific information-processing task. Digital systems vary in size and complexity from a few integrated circuits to a complex of interconnected and interacting digital computers. Digital system design invariably uses a modular approach. The modules are constructed from such digital components as registers, decoders, arithmetic elements, and control logic. The various modules are interconnected with common data and control paths to form a digital computer system.

Digital modules are best defined by the registers they contain and the operations that are performed on the data stored in them. The operations executed on data stored in registers are called microoperations. A microoperation is an elementary operation performed on the information stored in one or more registers. The result of the operation may replace the previous binary information of a register or may be transferred to another register. Examples vd orace this langual. of microoperations are shift, count, clear, and load. Some of the digital components introduced in Chap. 2 are registers that implement microoperations. For example, a counter with parallel load is capable of performing the micro-

microoperation

with language is a

-mic .aasoovq fanod.

writing symbols and

DEFERMINATION TO 9

In how expressing in

registers of a digital

latizable noitexinagu

used to tacilitate the

operations increment and load. A bidirectional shift register is capable of performing the shift right and shift left microoperations.

The internal hardware organization of a digital computer is best defined

by specifying:

1. The set of registers it contains and their function.

2. The sequence of microoperations performed on the binary information stored in the registers.

3. The control that initiates the sequence of microoperations.

It is possible to specify the sequence of microoperations in a computer by explaining every operation in words, but this procedure usually involves a lengthy descriptive explanation. It is more convenient to adopt a suitable symbology to describe the sequence of transfers between registers and the various arithmetic and logic microoperations associated with the transfers. The use of symbols instead of a narrative explanation provides an organized and concise manner for listing the microoperation sequences in registers and the control functions that initiate them.

The symbolic notation used to describe the microoperation transfers among registers is called a register transfer language. The term "register transfer" implies the availability of hardware logic circuits that can perform a stated microoperation and transfer the result of the operation to the same or another register. The word "language" is borrowed from programmers, who apply this term to programming languages. A programming language is a procedure for writing symbols to specify a given computational process. Similarly, a natural language such as English is a system for writing symbols and combining them into words and sentences for the purpose of communication between people. A register transfer language is a system for expressing in symbolic form the microoperation sequences among the registers of a digital computers in concise and precise manner. It can also be used to facilitate the design process of digital systems.

The register transfer language adopted here is believed to be as simple as possible, so it should not take very long to memorize. We will proceed to define symbols for various types of microoperations, and at the same time, describe associated hardware that can implement the stated microoperations. The symbolic designation introduced in this chapter will be utilized in subsequent chapters to specify the register transfers, the microoperations, and the control functions that describe the internal hardware organization of digital computers. Other symbology in use can easily be learned once this language has become familiar, for most of the differences between register transfer languages consist of variations in detail rather than in overall purpose.

register transfer language

odules that accom-

ms vary in size and

intenconnected and

ably uses a modular

tal components as

The various mod-

ins to form a digital

y contain and the

etions. A microsper-

manion stored in one

the previous binary

t reguler. Example

mora latigate soft to s

west makeroopers light

rough artificable

The operations

### 4-2 Register Transfer

register transfer

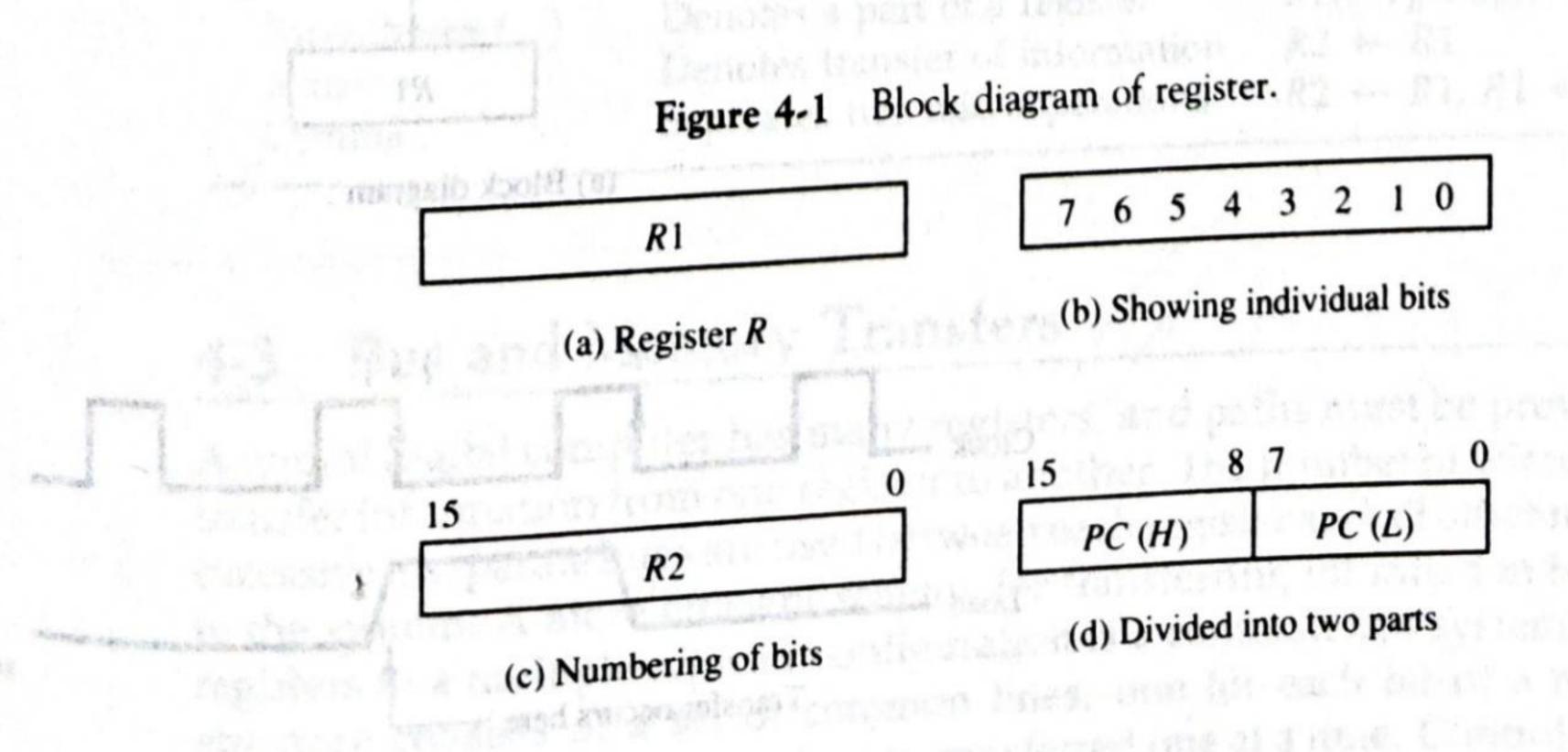

Computer registers are designated by capital letters (sometimes followed by numerals) to denote the function of the register. For example, the register that holds an address for the memory unit is usually called a memory address register and is designated by the name MAR. Other designations for registers are PC (for program counter), IR (for instruction register, and R1 (for processor register). The individual flip-flops in an n-bit register are numbered in sequence from 0 through n-1, starting from 0 in the rightmost position and increasing the numbers toward the left. Figure 4-1 shows the representation of registers in block diagram form. The most common way to represent a register is by a rectangular box with the name of the register inside, as in Fig. 4-1(a). The individual bits can be distinguished as in (b). The numbering of bits in a 16-bit register can be marked on top of the box as shown in (c). A 16-bit register is partitioned into two parts in (d). Bits 0 through 7 are assigned the symbol L (for low byte) and bits 8 through 15 are assigned the symbol H(for high byte). The name of the 16-bit register is PC. The symbol PC(0-7) or PC(L) refers to the low-order byte and PC(8-15) or PC(H) to the high-order byte.

Information transfer from one register to another is designated in symbolic form by means of a replacement operator. The statement

$R2 \leftarrow R1$

denotes a transfer of the content of register R1 into register R2. It designates a replacement of the content of R2 by the content of R1. By definition, the content of the source register R1 does not change after the transfer.

A statement that specifies a register transfer implies that circuits are available from the outputs of the source register to the inputs of the destination register and that the destination register has a parallel load capability. Nor-

distribute amount (d)

mally, we want the transfer to occur only under a predetermined control condition. This can be shown by means of an if-then statement.

If

$$(P=1)$$

then  $(R2 \leftarrow R1)$

control function

754/20-65.1d

stor Killights regulater K2. It dossignates

tire amitent of KI: By deminison, the

not change after the marsiet.

where P is a control signal generated in the control section. It is sometimes convenient to separate the control variables from the register transfer operation by specifying a control function. A control function is a Boolean variable that is equal to 1 or 0. The control function is included in the statement as follows:

$$P: R2 \leftarrow R1$$

The control condition is terminated with a colon. It symbolizes the requirement that the transfer operation be executed by the hardware only if P = 1.

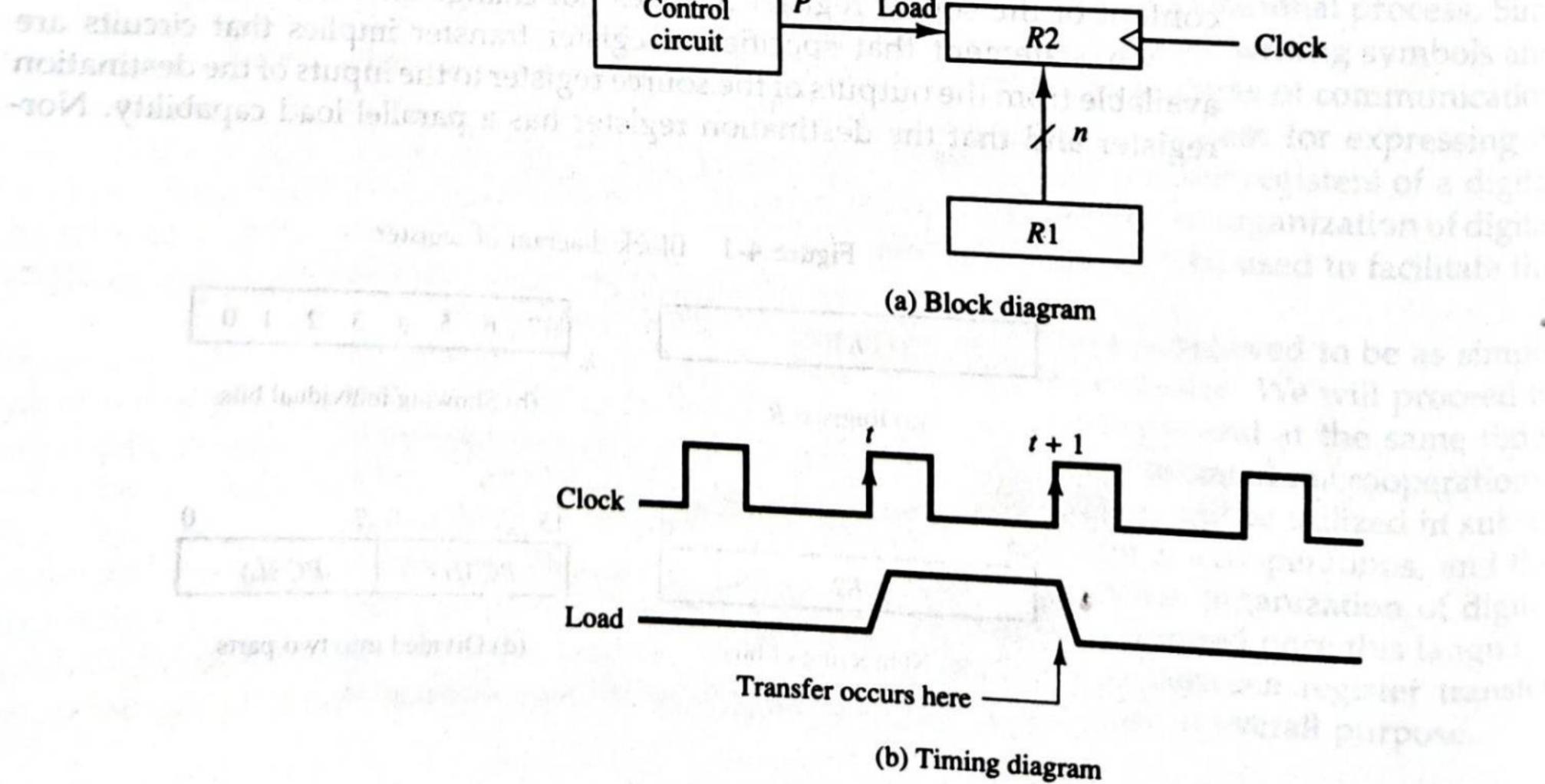

Every statement written in a register transfer notation implies a hardware construction for implementing the transfer. Figure 4-2 shows the block diagram that depicts the transfer from R1 to R2. The n outputs of register R1 are connected to the n inputs of register R2. The letter n will be used to indicate any number of bits for the register. It will be replaced by an actual number when the length of the register is known. Register R2 has a load input that is activated by the control variable P. It is assumed that the control variable is synchronized with the same clock as the one applied to the register. As shown

Figure 4-2 Transfer from R1 to R2 when P = 1.

Control

in the timing diagram, P is activated in the control section by the rising edge of a clock pulse at time t. The next positive transition of the clock at time t+1 finds the load input active and the data inputs of R2 are then loaded into the register in parallel. P may go back to 0 at time t+1; otherwise, the transfer will occur with every clock pulse transition while P remains active.

Note that the clock is not included as a variable in the register transfer statements. It is assumed that all transfers occur during a clock edge transition.

Even though the control condition such as P becomes active just after time t, the actual transfer does not occur until the register is triggered by the next

positive transition of the clock at time t+1.

Trure 4-3 Bus system for four registers

The basic symbols of the register transfer notation are listed in Table 4-1.

Registers are denoted by capital letters, and numerals may follow the letters.

Parentheses are used to denote a part of a register by specifying the range of bits or by giving a symbol name to a portion of a register. The arrow denotes a transfer of information and the direction of transfer. A comma is used to separate two or more operations that are executed at the same time. The statement

$$T: R2 \leftarrow R1, R1 \leftarrow R2$$

denotes an operation that exchanges the contents of two registers during one common clock pulse provided that T = 1. This simultaneous operation is possible with registers that have edge-triggered flip-flops.

TABLE 4-1 Basic Symbols for Register Transfers

| Symbol                         | Description                                                      | Examples                             |

|--------------------------------|------------------------------------------------------------------|--------------------------------------|

| Letters                        | Denotes a register                                               | MAR, R2                              |

| (and numerals) Parentheses ( ) | Denotes a part of a register                                     | R2(0-7), $R2(L)R2 \leftarrow R1$     |

| Arrow ← Comma,                 | Denotes transfer of information<br>Separates two microoperations | $R2 \leftarrow R1, R1 \leftarrow R2$ |

# 4-3 Bus and Memory Transfers

A typical digital computer has many registers, and paths must be provided to transfer information from one register to another. The number of wires will be excessive if separate lines are used between each register and all other registers in the system. A more efficient scheme for transferring information between registers in a multiple-register configuration is a common bus system. A bus registers in a multiple-register configuration in the system in the system and the system is a common bus system. A bus registers in a multiple-register configuration is a common bus system. A bus structure consists of a set of common lines, one for each bit of a register, structure consists of a set of common lines, one for each bit of a register, structure consists of a set of common lines, one for each bit of a register, structure consists of a set of common lines, one for each bit of a register, structure consists of a set of common lines, one for each bit of a register, structure consists of a set of common lines, one for each bit of a register, structure consists of a set of common lines, one for each bit of a register, structure consists of a set of common lines, one for each bit of a register, structure consists of a set of common lines, one for each bit of a register.

requirer for all data

bricons & and been a

MEDINATE OF CITATION

to the use of load and store instructions when communicating between mem ory and CPU. All other instructions are executed within the registers of the ory and CPU. All other instructions are experient for a RISC-type CPU consists of the CPU without referring to memory. A program for a RISC-type CPU consists CPU without referring to mentory. The base one memory and one regists of LOAD and STORE instructions that have three addresses the structions the structions that have three addresses the structions that have three addresses the structions that have three addresses the structions the structions that the structions that the structure three structures the structure three structures that the structure three structures the structure three structures that the structure three structures the structure three structures that the structure three structures the structure three structures three stru of LOAD and STOKE instructions that have three addresses with address, and computational-type instructions that have three addresses with tair amuras bus rete address, and computational-type liters. The following is a program to evaluate X = (A + B) \* (C + D).

| . LAIR TO THE TOTAL OF THE PARTY OF THE PART | $R1 \leftarrow M[A]$                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $R2 \leftarrow M[B]$                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $R \rightarrow M[C]$                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $R4 \leftarrow M[D]$                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R1 ← R1 + R2                                                               |

| RI, KI, KC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R3 ← R3 + R4                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R1 ← R1* R3                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

| X, R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $M[X] \leftarrow R1$                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R1, A<br>R2, B<br>R3, C<br>R4, D<br>R1, R1, R2<br>R1, R1, R2<br>R1, R1, R3 |

The load instructions transfer the operands from memory to CPU registers The add and multiply operations are executed with data in the registers without accessing memory. The result of the computations is then stored in memory with a store instruction. basic sand three she start and computer de

## Addressing Modes

The operation field of an instruction specifies the operation to be performed This operation must be executed on some data stored in computer registers or memory words. The way the operands are chosen during program execution is dependent on the addressing mode of the instruction. The addressing mode specifies a rule for interpreting or modifying the address field of the instruction before the operand is actually referenced. Computers use addressing mode techniques for the purpose of accommodating one or both of the following provisions:

- 1. To give programming versatility to the user by providing such facilitie as pointers to memory, counters for loop control, indexing of data, and program relocation. convert the excitession in

- 2. To reduce the number of bits in the addressing field of the instruction

the compatations instructions. The availability of the addressing modes gives the experienced assembly language programmer flexibility for writing programs that are more efficient with respect to the number of instructions and execution time.

To understand the various addressing modes to be presented in the section, it is imperative that we understand the basic operation cycle of the

Hindo-ni hejeppidon. In a branch typ-

computer. The control unit of a computer is designed to go through an instruction cycle that is divided into three major phases:

- 1. Fetch the instruction from memory.

- 2. Decode the instruction.

- 3. Execute the instruction.

an counter (PC)

There is one register in the computer called the program counter or *PC* that keeps track of the instructions in the program stored in memory. *PC* holds the address of the instruction to be executed next and is incremented each time an instruction is fetched from memory. The decoding done in step 2 determines the operation to be performed, the addressing mode of the instruction, and the location of the operands. The computer then executes the instruction and returns to step 1 to fetch the next instruction in sequence.

In some computers the addressing mode of the instruction is specified with a distinct binary code, just like the operation code is specified. Other computers use a single binary code that designates both the operation and the mode of the instruction. Instructions may be defined with a variety of addressing modes, and sometimes, two or more addressing modes are combined in one instruction.

An example of an instruction format with a distinct addressing mode field is shown in Fig. 8-6. The operation code specifies the operation to be performed. The mode field is used to locate the operands needed for the operation. There may or may not be an address field in the instruction. If there is an address field, it may designate a memory address or a processor register. Moreover, as discussed in the preceding section, the instruction may have more than one address field, and each address field may be associated with its own particular addressing mode.

Although most addressing modes modify the address field of the instruction, there are two modes that need no address field at all. These are the implied and immediate modes.

**Implied Mode:** In this mode the operands are specified implicitly in the definition of the instruction. For example, the instruction "complement accumulator" is an implied-mode instruction because the operand in the accumulator register is implied in the definition of the instruction. In fact, all register reference instructions that use an accumulator are implied-mode instructions.

Figure 8-6 Instruction format with mode field.

Belle to the property of the second of the s

MI. DOUGROUP OF THE TOTAL STORY OF BUILDING STR.

| 24-11-4-11 | Made | Address |

|------------|------|---------|

| Opcode     | Mode |         |

mented each time an

in step 2 determines

instruction, and the

ne instruction and

septembed Other

operation and the

variety of address-

es are combined in

dressing mode rield

e alion to be per-

eded for the opera-

ei saedt fi norbinie

Infocessor register

truction may have

be associated writing

reld of the instruc-

t all. These are the

outs of allientquit

-1006 insmalgmon'

- Uffacions said on bo

Zero-address instructions in a stack-organized computer are implied mode instructions since the operands are implied to be on top of the stack.

Immediate Mode: In this mode the operand is specified in the instruction itself. In other words, an immediate-mode instruction has an operand field rather than an address field. The operand field contains the actual operand to be used in conjunction with the operation specified in the instruction. Imme diate-mode instructions are useful for initializing registers to a constant value m counter or PC that

It was mentioned previously that the address field of an instruction may specify either a memory word or a processor register. When the address field specify either a memory work of a register mode, specifies a processor register, the instruction is said to be in the register mode.

> Register Mode: In this mode the operands are in registers that reside within the CPU. The particular register is selected from a register field in the instruc tion. A k-bit field can specify any one of 2k registers.

Register Indirect Mode: In this mode the instruction specifies a register in the CPU whose contents give the address of the operand in memory. In other words, the selected register contains the address of the operand rather than the operand itself. Before using a register indirect mode instruction, the programmer must ensure that the memory address of the operand is placed in the processor register with a previous instruction. A reference to the register is then equivalent to specifying a memory address. The advantage of a register indirect mode instruction is that the address field of the instruction uses fewer bits to select a register than would have been required to specify a memory address directly.

Autoincrement or Autodecrement Mode: This is similar to the register in direct mode except that the register is incremented or decremented after or before) its value is used to access memory. When the address stored in the register refers to a table of data in memory, it is necessary to increment or decrement the register after every access to the table. This can be achieved by using the increment or decrement instruction. However, because it is such common requirement, some computers incorporate a special mode that auto matically increments or decrements the content of the register after data access

The address field of an instruction is used by the control unit in the CP to obtain the operand from memory. Sometimes the value given in the address field is the address of the operand, but sometimes it is just an address from which the address of the operand is calculated. To differentiate among various addressing modes it is necessary to distinguish between the addressing modes it is necessary to distinguish between the addressing modes it is necessary to distinguish between the addressing modes it is necessary to distinguish between the addressing modes it is necessary to distinguish between the addressing modes it is necessary to distinguish between the addressing modes it is necessary to distinguish between the addressing modes it is necessary to distinguish between the addressing modes it is necessary to distinguish between the addressing modes it is necessary to distinguish between the addressing modes it is necessary to distinguish between the addressing modes it is necessary to distinguish between the addressing modes it is necessary to distinguish between the addressing modes it is necessary to distinguish between the addressing modes it is necessary to distinguish between the addressing modes it is necessary to distinguish between the addressing modes it is necessary to distinguish the addressing modes and the addressing modes it is necessary to distinguish the addressing modes and the part of the instruction and the effective address used by the control when executing the instruction. The effective address is defined to be the memor address obtained from the computation dictated by the given addressing mode. The effective address is the address of the operand in a computation

effective address

branch-type instruction. We have already defined two addressing modes in Chap. 5. They are summarized here for reference.

Direct Address Mode: In this mode the effective address is equal to the address part of the instruction. The operand resides in memory and its address is given directly by the address field of the instruction. In a branch-type instruction the address field specifies the actual branch address.

Indirect Address Mode: In this mode the address field of the instruction gives the address where the effective address is stored in memory. Control fetches the instruction from memory and uses its address part to access memory again to read the effective address. The indirect address mode is also explained in Sec. 5-1 in conjunction with Fig. 5-2.

A few addressing modes require that the address field of the instruction be added to the content of a specific register in the CPU. The effective address

in these modes is obtained from the following computation:

actions must

May Interessed

effective address = address part of instruction + content of CPU register

The CPU register used in the computation may be the program counter, an index register, or a base register. In either case we have a different addressing mode which is used for a different application.

Relative Address Mode: In this mode the content of the program counter is added to the address part of the instruction in order to obtain the effective address. The address part of the instruction is usually a signed number (in 2's complement representation) which can be either positive or negative. When this number is added to the content of the program counter, the result produces an effective address whose position in memory is relative to the address of the next instruction. To clarify with an example, assume that the program counter contains the number 825 and the address part of the instruction contains the number 24. The instruction at location 825 is read from memory during the fetch phase and the program counter is then incremented by one to 826. The effective address computation for the relative address mode is 826 + 24 = 850. This is 24 memory locations forward from the address of the next instruction. Relative addressing is often used with branch-type instructions when the branch address is in the area surrounding the instruction word itself. It results in a shorter address field in the instruction format since the relative address can be specified with a smaller number of bits compared to the number of bits required to designate the entire memory address.

Indexed Addressing Mode: In this mode the content of an index register is added to the address part of the instruction to obtain the effective address. The

264

- mora secues mean-

radices amoda is also

idd of the maintenion

Spann the effective

ersed aumber (in 2's

of negative. When

enter Hare terral pro-

e to the address

hat the program

cauch-type instruc-

brow negomient un

ent torniat since the

bits companed to the

an index regulator is

estective address. Her

index register is a special CPU register that contains an index value. The index register is a special Cro register the beginning address of a data and address field of the instruction defines the beginning address of a data and in memory. Each operand in the array is stored in memory relative to the beginning address. The distance between the beginning address and the beginning address. The distance value stored in the index register. And address of the operand is the index value stored in the index register. And wife of lauge of Praise operand in the array can be accessed with the same instruction provided the the index register contains the correct index value. The index register can be incremented to facilitate access to consecutive operands. Note that if an index type instruction does not include an address field in its format, the instruction converts to the register indirect mode of operation. simiountess soft to his

Some computers dedicate one CPU register to function solely as an inde terring by training or hason register. This register is involved implicitly when the index-mode instruction is used. In computers with many processor registers, any one of the CPI registers can contain the index number. In such a case the register must be specified explicitly in a register field within the instruction format.

> Base Register Addressing Mode: In this mode the content of a base register is added to the address part of the instruction to obtain the effective address This is similar to the indexed addressing mode except that the register is now called a base register instead of an index register. The difference between the two modes is in the way they are used rather than in the way that they are computed. An index register is assumed to hold an index number that relative to the address part of the instruction. A base register is assumed to ho a base address and the address field of the instruction gives a displacement relative to this base address. The base register addressing mode is used computers to facilitate the relocation of programs in memory. When program and data are moved from one segment of memory to another, as required multiprogramming systems, the address values of instructions must refle this change of position. With a base register, the displacement values instructions do not have to change. Only the value of the base register require updating to reflect the beginning of a new memory segment.

### Numerical Example

To show the differences between the various modes, we will show the effe of the addressing modes on the instruction defined in Fig. 8-7. The two-wo instruction at address 200 and 201 is a "load to AC" instruction with an addre field equal to 500. The first word of the instruction specifies the operation co and mode, and the second word specifies the address part. PC has the val 200 for fetching this instruction. The content of processor register R1 is 4 and the content of an index register XR is 100. AC receives the operand at the instruction is executed. The figure lists a few pertinent addresses a shows the memory content at each of these addresses.