### Introduction 17.1

Explain about any DMA Controller.

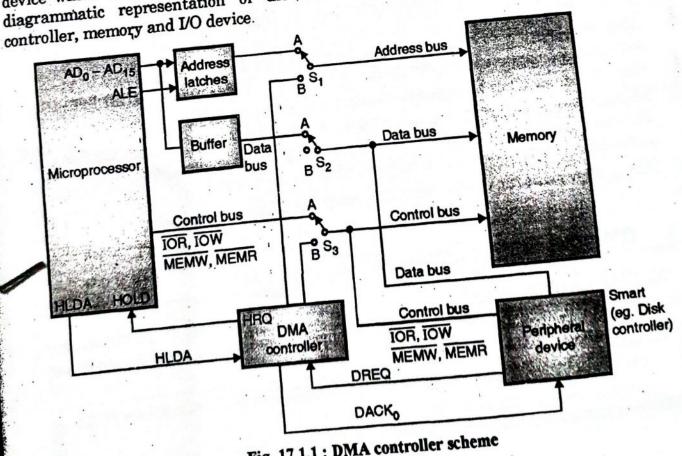

In I/O data transfer, data is transferred, by using microprocessor. microprocessor will read data from I/O device and then will write data to memory. In this case, there are two operations for single data transfer. If the data is less, then microprocessor will not waste its time; transferring data from I/O to memory or back. But suppose, data is huge, then the transfer rate from I/O to memory or back will slow down because of microprocessor intervention. In such case, to speed up the process of transferring the data, we can think, Can I/O have direct access to memory ?; and the answer is, yes. It can have Direct memory access (DMA), but under Supervision. The device which supervises, data transfer is named as DMA controller. Now let's have diagrammatic representation of the scheme, which depicts microprocessor, DMA

Fig. 17.1.1: DMA controller scheme

### Let's understand the concept clearly.

- Initially, switches S<sub>1</sub>, S<sub>2</sub> and S<sub>3</sub> are at position A.

- 2. No direct access to memory by I/O.

- 3. Microprocessor is MASTER of all three buses; address, data and control.

- 4. Microprocessor treats DMA controller, as I/O device ONLY.

- 5. Using IN/OUT instruction, you can program DMA controller chip, for various modes.

- 6. Whenever, peripheral device is ready to transfer data, DIRECTLY to memory, it will generate REQUEST (DRQ → DMA REQUEST), to DMA controller, asking for direct access.

- 7. In response to DRQ, DMA controller will activate, HRQ (HOLD request), connected to HOLD pin of microprocessor. By activating HOLD line, DMA controller request microprocessor, to HOLD for sometime and allow him to become a master of all three buses.

- 8. Moment HOLD pin is HIGH, microprocessor will complete the present job and also activate HLDA (HOLD acknowledge) signal; informing, DMA controller to become master.

- Microprocessor tristates, all its buses, so total cutoff from memory and I/O device.

Thus microprocessor relinquishes the buses and provides control to DMA controller.

- 10. Now DMA controller is master. It will position all three switches to position B.

- 11. DMA controller will also generate DACK (DMA acknowledge) signal to peripheral device; informing that, direct access is allowed.

- 12. Now it will generate address and control signal. Data will flow from memory to I/O or vice versa.

- 13. After completing data transfer, DMA controller will deactivate HOLD line. It also positions, switches back to position A.

- 14. Now microprocessor will regain the control over the three buses.

- 15. Microprocessor will start executing instructions from main program. Till DMA is inactive or not master of the bus, is referred as DMA IDLE Cycle. When DMA controller gains the control, it is referred as DMA Active Cycle.

This is about basics of DMA. Now let's study the different methods of transferring data.

### 17.2 DMA Controller: Data Transfer Modes

The DMA controller functions as a bus master and bus slave. It performs data transfer operations. DMA controlled input/output is further divided into the following categories:

- Transparent or Hidden DMA.

#### Burst or Block Transfer DMA 17.2.1

- It is the fastest DMA mode.

- In this mode, two or more data bytes are transferred continuously.

- The microprocessor is disconnected from the system bus during DMA transfer i.e. the microprocessor cannot executes its own program during this transfer.

- N number of DMA cycles are added into the machine cycles of the microprocessor where N is number of bytes to be transferred.

- In this mode, the DMA controller sends 'HOLD' signal to the microprocessor and waits for HLDA signal.

- After receiving HLDA signal, the DMA controller gains control of the system bus and executes a DMA cycle to transfer one byte.

- After transferring one byte, it increments memory address, decrements counter and transfers next byte.

- In this way, it transfers all data bytes between memory and I/O devices. After transferring all data bytes, the DMA controller disables 'HOLD' signal and enters into slave mode.

#### Cycle Steal or Single Byte Transfer DMA 17.2.2

- In cycle steal transfer only one byte of data is transferred at a time.

- This type of DMA is slower than burst DMA.

- In this mode, only one DMA cycle is added between two machine cycles of the microprocessor, hence the instruction execution speed of the microprocessor is reduced slightly.

- In this mode the DMA controller sends 'HOLD' signal to the microprocessor and waits for HLDA signal.

- After receiving HLDA signal, the DMA controller gains control of the system bus and executes only one DMA cycle.

- After transferring one byte, it disables 'HOLD' signal and enters into slave mode.

- The microprocessor then gains control of the system bus and executes next machine cycle. If the count is not zero and next data is available then the DMA controller sends 'HOLD' signal to the microprocessor and transfers next byte of data block.

#### Transparent or Hidden DMA Transfer 17.2.3

- The microprocessor executes some states during which it floats the address and data buses.

- During these states, the microprocessor is isolated from the system bus.

- The DMA controller transfers data between memory and I/O devices during these states. This operation is transparent to microprocessor.

10 poquomar. In the Britis

Is abou

480-0E

This is the slowest DMA transfer, In this mode, the instruction execution speed of microprocessor is not reduced. But, the transparent DMA requires logic to detect the states when the microprocessor is floating the buses.

Now, we will study DMA controller chip 8237.

## 17.3 8237 High Performance Programmable DMA Controller

### 17.3.1 Features

- It provides various modes of DMA.

- It provides on chip four independent DMA channels. The number of channels can be increased by cascading DMA controller chips.

- Each channel can be used in auto initialization mode.

- It can transfer data between two memory blocks in DMA mode i.e. memory to memory transfer.

- In memory to memory transfer a single word can be written into all location of memory block.

- The address of memory is either incremented or decremented after each DMA cycle depending upon the mode.

- The clock frequency is 3 MHz (8237) or 5 MHz (8237-2).

- The data transfer rate is very high e.g. 1.6 M bytes/second for 8237-2 at 5 MHz.

- Directly expandable to any number of channels. It doesn't require any additional chip for cascading. There is no limitations on cascading.

- It provides EOP line that is used to terminate DMA operation. This signal can be generated by external hardware.

- The DMA can be requested by setting an appropriate bit of request register.

- Independent control for DREQ and DACK signal. DREQ and DACK signals can be initialized either for active high or active low.

- It provides compressed timings to improve throughput of the system. It can compress the transfer time to two cycles (2S).

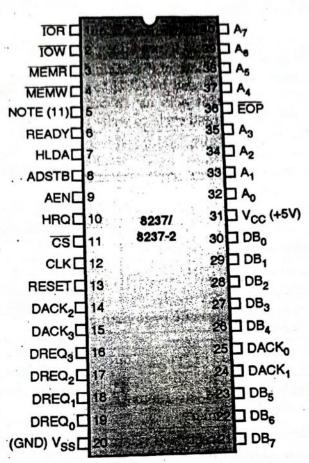

### 17.4 Pin Configuration of 8237

- Q. 1 Draw and explain pin configuration of 8237.

- Q. 2 Explain the significance of AEN, ADSTB, EOP, READY pins of 8237.

Fig. 17.4.1: Pin configuration of 8237

| Symbol                            | Description                                                                                                                                                                                        |  |  |  |  |  |  |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| CLK                               | This is a clock input line ignored in slave mode. In master mode, this signal controls all internal and external DMA operations. The data transfer rate depends upon the frequency of this signal. |  |  |  |  |  |  |  |

| $\overline{\mathbf{c}}\mathbf{s}$ | In slave mode, this signal is generated by address decoder to select 8237 chip for communication between CPU and 8237. In master mode this signal is ignored.                                      |  |  |  |  |  |  |  |

| Reset                             | It is an asynchronous input line. This signal clears the command, status, request and temporary register and forces 8237 into slave                                                                |  |  |  |  |  |  |  |

| READY                             | In master mode, this signal is used to add wait states into a DMA cycle.                                                                                                                           |  |  |  |  |  |  |  |

| HRQ                               | It is a hold request output line. It is connected to hold input of the CPU. It is used to request control of the system bus.                                                                       |  |  |  |  |  |  |  |

| HLDA                              | It is a hold acknowledge input line. This signal is generated by CPU. In response to this signal, the 8237 gains control of the system bus and enters into master mode.                            |  |  |  |  |  |  |  |

| IOR                               | It is an active low bi-directional tristate line. In slave mode, it act as an input line and used to read contents of 8237 registers. I                                                            |  |  |  |  |  |  |  |

| Microprocessors & Int             | Description output line. This signal is general                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Symbol                            | Description  master mode, it acts as an output line. This signal is generated during DMA cycle to read data from I/O device.  It is an active low bi-directional line. In slave mode, it acts as an input line and used by CPU to write contents to 8237 registers. In master mode, it acts as an output line. This signal is generated master mode, it acts as an output line. This signal is generated during DMA read cycle to write data into I/O device. |  |  |  |  |  |  |  |  |

| **                                | during DMA read cycle to write data into I/O device.                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| A <sub>0</sub> - A <sub>2</sub>   | master mode, the 8237 provides lower bits of memory address on                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| A4 - A7                           | these lines.  These are tristate address output lines. These lines are tristated in slave mode. In master mode, the 8237 transfers bits of memory address on these lines.                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| MEMR                              | It is an active low tristate control output line. It is tristated in slave mode. In master mode, this signal is generated during DMA read cycle or during memory to memory transfer cycle to read contents of                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| MEMW                              | It is an active low tristate output line. It is tristated in slave mode. In master mode, this signal is activated during DMA write or during memory to memory transfer cycle to write data into destination memory.                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| DB <sub>0</sub> - DB <sub>7</sub> | These are bi-directional tristate buffered data lines. In slave mode, these lines are used to transfer data between CPU and 8237's registers. In master mode, these lines act as address output lines. The 8237 places higher byte of address on these lines during DMA cycles.                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| AEN                               | This active high output enables the 8 bit latch that drives the upper 8 bit address bus. The AEN pin is used to disable other bus drivers during DMA transfers.                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| ADSTB<br>Address<br>Strobe)       | This output line is used to strobe the upper address byte generated by 8237 in master mode into an external latch.                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| DREQ, -DREQ <sub>3</sub>          | These are asynchronous DMA channel request lines used by peripheral. The polarity of each signal is programmable i.e. these lines can be used as either active high or active low input. DREG must be maintained until the corresponding DACK is activated.                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| OACK, - DACK,                     | These are DMA acknowledge output lines. The polarity of each line is programmable. This signal indicates that the requesting peripheral has been granted for DMA cycle.                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| ОP                                | End of Process: It is an active low bi-directional signal. This line is also used to terminate DMA cycle. The DMA cycle can be terminated by pulling <b>EOP</b> input low. The 8237 also generate EOP pulse, when the terminal count for any channel is reached.                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

17.5

Q.

and in

RESE

REAL CLO

ADS MEN

MEN

IC

DRE DRE HI DAC DAC

823

of r

(1)

Controller

nerated

s as an

ters. In

ierated

e lines

237. In

ess on

ted in

emory

slave

read

ents of

mode.

ite or

into

mode,

8237's

lines.

DMA

upper

rivers

erated

ed by

these

REQ

h line

sting

ine is

n be

rates

Block Diagram of 8237

### 17.5

Draw and explain the block diagram of 8237 DMA. The Fig. 17.5.1 shows an internal block diagram of 8237. It consists of logic blocks Q.

and internal register. Ino/Decrementer Decrementer Temp address I/O buffer Temp word **EOP** ◆ reg(16) pount reg(16) RESET cs 16 bit bus Output buffer READY-16 bit bus CLOCK-Bead / Write buffer Timing Read buffer and AEN 4 Current control Base Base Current ADSTB ◀ word address count address count MEMR ◆ Command (16)(16) (16) (16) =MEMW ◀ control IOR ◀ D0-D1 **IOW** ◀ Write buffer Read buffer DREQ<sub>0</sub>-1/O buffer DB<sub>0</sub>-DB<sub>7</sub> Command (8) Priority DREQ3 encoder HLDA Mask (4) and rotating Read write HRQ ◀ priority Mode (4x8) Status (8) Temporary (8) DACK<sub>0</sub>- ◀ logic. Request (4) DACK<sub>3</sub>

Fig. 17.5.1: Internal block diagram of 8237

### 8237 Registers

It contains 344 bits of internal memory in the form of registers. It contains 12 types of registers.

- Current address register

- Base address register

- Command register

- Request register

- Status register

- Current word register

- Base count register

- Mode register

- Mask register

- Temporary register

#### Current address register (1)

Each channel has a 16 bit current address register.

This register holds the address of memory location to be accessed during current DMA cycle. The address stored in the location to be accessed during current of the address stored in the location to be accessed during current of the location of the location to be accessed during current of the location of the location to be accessed during current of the location o DMA cycle. The address stored in this register is automatically incremented of

- It is a read and write register.

- It is divided into two parts : lower byte and higher byte.

ring these

s and data

DIOCK. controller machine; mode.

stem pns

ssor and

SE TOSSOS s of the

d enters s. After

ter and

em pna

sor and

OC62201.

ransier

ntroller

17-8

8237 DMA Controller

In autoinitialization mode, it is initialized automatically with original address after  $\overline{EOP}$  signal. The current address register format is as shown in Fig. 17.5.2.

# A15 A14 A13 A12 A11 A10 A9 A8 A7

Fig. 17.5.2: Current address register

Current word register

9.2

1.0

'ZI

T

Each channel has a 16 bit current word count register.

The original value stored in this register indicates the number of bytes to be transferred.

The word count is decremented after each transfer. The current count indicates the numbers of pending transfers.

When the count value in the register goes to zero, a TC will be generated. It is a read and write register. It is also divided into two parts: lower byte and higher byte.

In autoinitialization mode, this register is initialized automatically with original count value after EOP signal. The current word register format is as shown in Fig. 17.5.3.

W15 W14 W13 W12

Fig. 17.5.3: Current word register

Base address register

Each channel has a 16 bit base address register.

It holds original value of address during all DMA transfers i.e. the contents of this It is a write only register. register is not updated during DMA transfers.

When  $\overline{EOP}$  is activated, the 8237 transfers contents of base address registers into current address register in autoinitialization mode.

This register is written along with current address register during initialization. Format is same as current address register.

Base count register (4)

Each channel has a 16 bit base word count register.

It holds original count value during all DMA cycle i.e. the contents of this register

When EOP is activated, the 8237 transfers contents of this register into current

This register is written along with current address register during initialization. Format is same as current word register.

Microprocessors &

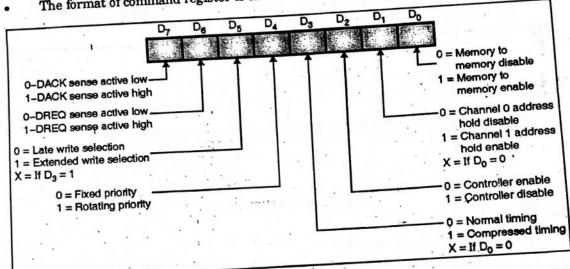

Comman It is an 8

> This reg 8237.

The form

0-DACK a 1-DACK se

X = # 02 = 1

It

0=

Command register

ter

the

ead

inal

this

into

tion.

ister

rent

tion.

It is an 8 bit control register. It is a write only register.

This register is cleared by reset signal. It is used to initialize operation modes of

The format of command register is as shown in Fig. 17.5.4.

Fig. 17.5.4: Command register

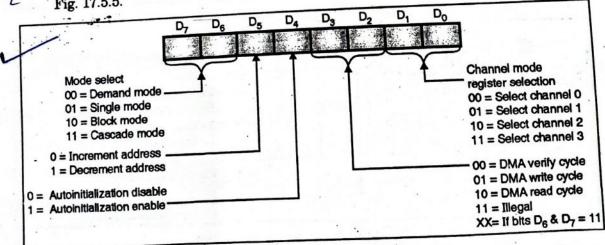

(6) Mode register

- It is an 8 bit write only register.

- It is used to set operating modes of 8237.

- Each channel has a 6 bit mode register.

- All registers are cleared by reset signal. The format of mode register is as shown in Fig. 17.5.5.

Fig. 17.5.5: Mode register

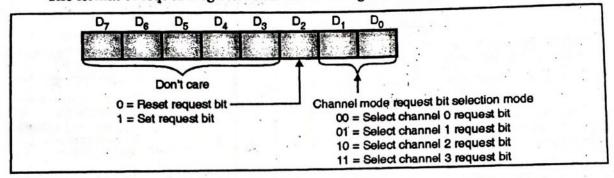

#### Request register (7)

It is an 8 bit write only register.

It is used to request DMA through software. Each channel has a request bit associated with it in the 4 bit request register.

Each register bit is set or reset separately under software control. The request is automatically cleared after TC. It is also cleared by external EOC signal.

- This register is cleared by reset signal.

- Software request will be serviced only if the channel is in block mode.

- In memory to memory transfer, the software request for channel 0 should be set.

The format of request register is as shown in Fig. 17.5.6.

Fig. 17.5.6: Request register

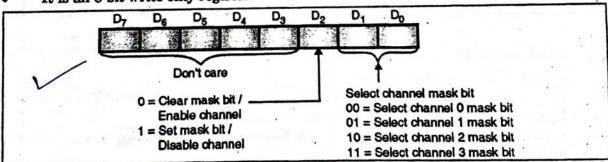

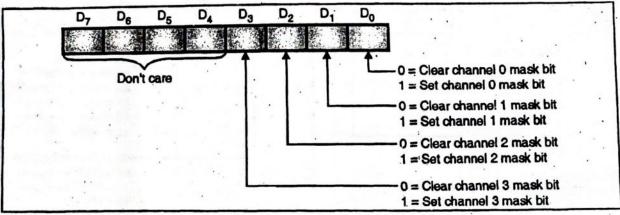

### (8) Mask register

• It is an 8 bit write only register.

Fig. 17.5.7: Byte written mask register

Fig. 17.5.8: Bit written mask register

It is used to maskout the channel DMA request.

Controller

est bit

uest is

be set.

In normal mode, mask bit is set automatically after TC. It is not affected in autoinitialization mode.

The reset signal sets mask bit of all channels i.e. it disables all channels.

The channel mask bit is selected by  $D_1$  and  $D_0$  bits of the mask format as shown in Fig. 17.5.7. Each bit of the 4 bit mask register can be set or reset separately under software control.

All 4 bits of the mask register may also be written with a single command as shown in Fig. 17.5.8.

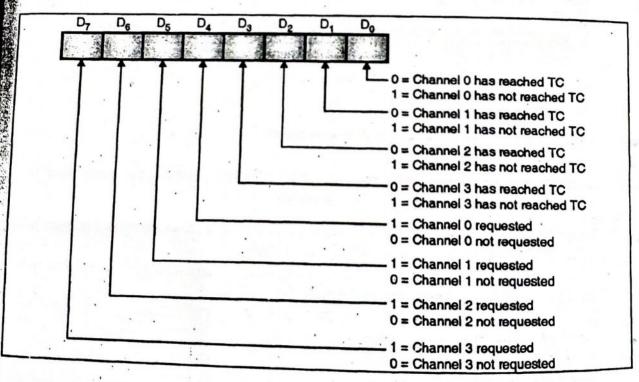

#### Status register (9)

It is an 8 bit read only register.

Microprocessors & Interfacing (MDU)

It indicates which channels have reached a terminal count and which channels have pending DMA requests.

Bits 0-3 are set every time a TC is reached by that channel or external EOP signal is applied.

These bits are cleared automatically on reading the status register and upon reset signal.

Bits 4-7 are set whenever their corresponding channel is requesting service. The format of status register is as shown in Fig. 17.5.9.

Fig. 17.5.9: Status register

### (10) Temporary register

- This register is used to hold data during memory to memory transfer.

- It is an 8 bit read only register.

- The microprocessor can read last byte of memory to memory transfer.

- It is cleared by reset signal.

noireool WO.

dingy AD

of Croms

Brid

10 B

T Of

Microprocess

Channel

- (11) Software commands These are additional special write only software commands.

- These commands do not require a specific data pattern. i.e. writing only data into corresponding address enables such commands.

- (12) Clear first / last flip-flop

- This command is used to reset internal first / last flip-flop.

- After issuing this command the microprocessor can access lower byte of any 16 bit register. The F/L flip-flop is toggled after each read or write 16 bit register.

- (13) Master clear

- It is a software reset command.

- It clear command, status, request, temporary registers and F/L flip-flop.

- It sets mask register and forces 8237 in slave mode.

- The Tables 17.5.1 and 17.5.2 shows addresses of all registers.

Table 17.5.1: Software command codes

|    | ing.           |              | Sign | ıals  | e en la repre | Operation                      |  |  |  |

|----|----------------|--------------|------|-------|---------------|--------------------------------|--|--|--|

| A, | A <sub>2</sub> | At A IOR IOW |      | IOW   |               |                                |  |  |  |

| 1  | 0              | 0            | 0.   | 0     | 1             | Read Status Register           |  |  |  |

| 1  | 0              | 0            | 0    | 1     | 0             | Write Command Register         |  |  |  |

| 1  | 0              | 0            | 1    | 0     | 1             | Illegal                        |  |  |  |

| 1  | 0              | 0            | 1    | - 1   | . 0           | Write Request Register         |  |  |  |

| 1  | 0              | 1            | 0    | - 0   | 1             | Illegal                        |  |  |  |

| 1  | 0              | 1            | 0    | - 1   | 0             | Write Single Mask Register Bit |  |  |  |

| 1  | 0              | 1            | 1    | 0     | 1             | Illegal                        |  |  |  |

| 1  | 0              | 1            | 1    | 1     | 0             | Write Mode Register            |  |  |  |

| 1  | 1              | 0            | 0    | 0     | 1             | Illegal                        |  |  |  |

| 1  | 1              | 0            | 0    | 1     | 0             | Clear Byte Pointer Flip-Flop   |  |  |  |

| 1  | 1              | 0            | 1    | 0     | 1             | Read Temporary Register        |  |  |  |

| 1  | 1              | 0            | 1    | - 1 - | 0             | Master Clear                   |  |  |  |

| 1  | 1              | 1            | 0    | 0     | 1             | Illegal                        |  |  |  |

| 1  | 1              | 1            | 0    | 1     | 0             | Clear Mask Register            |  |  |  |

| 1  | 1              | 1            | 1    | 0     | 1             | Illegal                        |  |  |  |

| 1  | 1              | 1            | 1    | 1     | 0             | Write All Mask Register Bits   |  |  |  |

unt and address register command codes

| annel | Register                | Operation |                |          | Sign   | F A | A | A  | A   | Internal .<br>Flip-Flop | COLUMN TO SERVICE SERV |

|-------|-------------------------|-----------|----------------|----------|--------|-----|---|----|-----|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Base and<br>Current     | Write     | <b>CS</b><br>0 | 10R<br>1 | 0<br>0 | 0   | 0 | 0, | 0 0 | 0<br>1                  | A <sub>0</sub> - A<br>A <sub>6</sub> - A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       | Address Current Address | Read      | 0              | 0        | 1      | 0   | 0 | 0  | 0   | 0                       | A <sub>0</sub> - A<br>A <sub>6</sub> - A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

2

3