### What does an offset tell us?

The offset is a 16 bit hex number contained by the instruction pointer (I.P.) register and it tells BIU the location in the code segment, from which the next instruction byte is to be fetched.

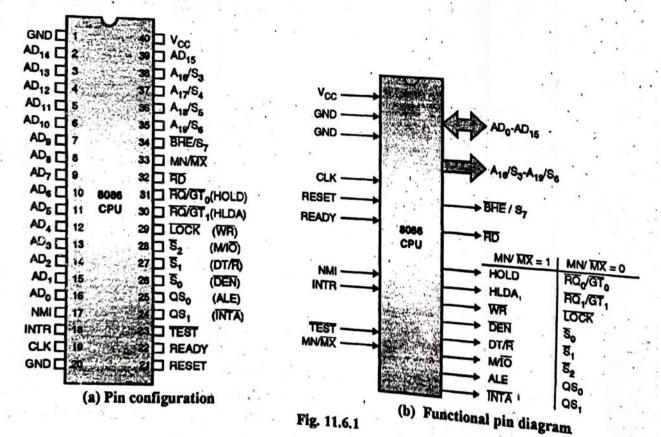

### 11.6 Pin Diagram of 8086

| r. No. | Pins                                                            | Name of the pins                                                                                                                                                                                                         |

|--------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.     | Supply pins (3 pins)                                            | V <sub>cc</sub> GND GND                                                                                                                                                                                                  |

| 2.     | Clock related pins (3 pins)                                     | CLK<br>RESET<br>READY                                                                                                                                                                                                    |

| 3.     | Address and Data pins (21 pins)                                 | $AD_0 - AD_{15}$<br>$A_{16}/S_3 - A_{19}/S_6$<br>$\overline{BHE} / S_7$                                                                                                                                                  |

| 4.     | Interrupt pins (2 pins)                                         | NMI<br>INTR                                                                                                                                                                                                              |

| 5.     | Other control (3 pins)                                          | TEST MN/MX RD                                                                                                                                                                                                            |

| 6.     | Mode multiplexed signals (8 pins) (MIN mode – MAX mode signals) | $\begin{aligned} &\text{HOLD} - \overline{RQ}_0 \ / \ \overline{GT}_0 \\ &\text{HLDA} - \overline{RQ}_1 \ / \ \overline{GT}_1 \\ &\overline{WR} \ - \overline{LOCK} \\ &\overline{DEN} \ - \overline{S}_0 \end{aligned}$ |

|        |                                                                 | $DT/\overline{R} - \overline{S_1}$ $M/\overline{IO} - \overline{S_2}$ $ALE - QS_0$ $\overline{INTA} - QS_1$                                                                                                              |

#### Supply pins (3 pins)

| Vcc | GND            | GND           | 1  |

|-----|----------------|---------------|----|

|     | a Color Care A | A PROPERTY OF | ď, |

- Used for power supply i.e. +5V on Vcc w.r.t. GND.

- Two separate GND pins for two layers of 8086 chip, improves the noise rejection.

#### Clock related pins (3 pins) II.

| CLK | RESET | RI    | MANY    |

|-----|-------|-------|---------|

|     |       | 3-167 | TITLE I |

#### CLK

- This pin provides the basic timing for the processor.

- 8086 does not has an on-chip clock generator hence an external clock generator like 8284 is used to provide the clock signal.

- It is asymmetric with 33% duty cycle, TTL clock signal.

#### RESET

- It causes the processor to immediately terminate its present activity. The 8284 clock generator provides this signal.

- This signal must be active high for atleast 4 clock cycles

- It clears all the flag register, the Instruction Queue, the DS, SS, ES and IP registers and sets the bits of CS register.

- Hence the reset vector address of 8086 is FFFF0H (as CS = FFFFH and

#### READY

Microprocessors & Interfacing (MDU) It is an acknowledgement from the addressed memory or I/O that it is an acknowledgement specially meant for slow devices.

It is an acknowledge specially meant for slow devices. complete the data and Ta of a M/C cycle, uP samples the READY input between T2 and T3 of a M/C cycle.

μP samples the READY input seems wait-states between T2 and T3, until READY pin is LOW, μP inserts wait-states between T2 and T3, until READY WIGH

becomes HIGH.

## Address and data pins (21 pins)

| Address  | Section Control of the Control | 1 - 6 - 6 - 6 - 6 - 6 - 6 - 6 - 6 - 6 - |

|----------|--------------------------------|-----------------------------------------|

| AD - ADo | A16/S3 A16/S6                  | BHE/S7                                  |

| ADI6-120 | with the state of              |                                         |

#### AD18 - AD0

These are time multiplexed data address lines i.e. for some time they have address and for some time data

It gives the address  $A_{16}$  –  $A_0$  during T1 of an Machine Cycle. (When ALE = 1)

It gives the data D<sub>15</sub> - D<sub>0</sub> after T1 of an M/C Cycle (Machine cycle).

#### A16/Ss ... A16/S6

These lines work as Address bus (A<sub>16</sub> ... A<sub>19</sub>) during T1 of every M/C Cycle.

T2 onwards these lines work as Status signals S<sub>3</sub> ... S<sub>6</sub>.

S3 and S4 gives the status of the memory segment currently accessed. S6 gives the status of the Interrupt Enable Flag updated every clock cycle. Se goes by when 8086 controls the shared system bus.

|   | S <sub>4</sub> | S <sub>3</sub> | Segment accessed     |

|---|----------------|----------------|----------------------|

| r | 0              | 0              | Extra Segment        |

| r | 0              | 1              | Stack Segment        |

| r | 1              | . 0            | Code Segment or None |

| r | 1              | 1              | Data Segment         |

# BHE/S, Bus High enable

- This line carries the BHE signal during T1.

- BHE and Ao are used together to access a word/byte from the memory is shown in the banking in section 11.8.

- Status line S7 is reserved for "further development".

### Interrupt pins (2 pins)

| NM   | Mit. | 母子 | T | TID |

|------|------|----|---|-----|

| 1111 | 1    | 4  | 2 | IT  |

#### NMI

This is a non-maskable, edge triggered that causes type 2 interrupt in transfers in receiving an interrupt on NMI line, the μP executes INT 2 and transfers control to location 2 \* 4 =00000077. control to location 2 \* 4 = 00008H in the Interrupt Vector Table (IVT). It reads Microprocessors & Interfacing (MDU) locations starting from this address to get values for IP and CS of the ISR

11-24

It is not maskable internally by software.

A transition from LOW to HIGH on this pin, causes the interrupt at the end of the current instruction

- This is a non-vectored, maskable, level triggered interrupt sampled during last INTR clock cycle of each instruction.

- To get the vector number for the interrupt the following procedure is followed

- On receiving an interrupt on INTR line, the µP executes 2 INTA pulses.

- First INTA pulse → the interrupting device is indicated for its interrupt being accepted while the device calculates the vector number.

- Second INTA pulse → the interrupting device sends the vector number to the microprocessor on the data lines.

- Control shifts to location pointed by IP and CS which are loaded from IVT at Vector No \* 4.

### Other control (3 pins)

| HOUSE SERVICE | 16175 | A 15 15 15 15 15 15 15 15 15 15 15 15 15         |

|---------------|-------|--------------------------------------------------|

| TEST          | MN/M  | X RD                                             |

| TEST          | MILLY | SEC. SEC. AND DESCRIPTION OF THE PERSON NAMED IN |

#### TEST

- It is an active low input line dedicated for 8087 Co-processor.

- In minimum mode it is connected to GND. In Maximum Mode whenever the Co-processor is busy it makes this pin HIGH.

- TEST input is examined by the WAIT instruction.

- If the TEST pin is high, the µP enters idle state, till TEST pin becomes low i.e. 8087 is free.

#### MN/MX

- This is an input signal to 8086 that indicates the processor has to work in which mode.

- If this signal is HIGH, 8086 is in Minimum mode i.e. Single-processor system.

- If this signal is LOW, 8086 is in Maximum mode i.e. Multiprocessor system.

#### RD

It is an active low output signal. When it is low 8086 reads from memory or an I/O device.

# VI. Mode multiplexed signals (8 pins) (MIN Mode — Max Mode Signals)

| A STATE OF THE STA | September 1 | (MIN MO          | de — Max Mo     | de Signals | 1                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------|-----------------|------------|-------------------|

| HOLD - RE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CT LANGE    | -                |                 |            | SECTION AND LOCAL |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | OCTO EILDY  | - RQ RT          | ewro Late       | 8105120100 | -                 |

| DT/R o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Sec. 12.    |                  |                 |            | Fig. 29           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MIO-        | - S <sub>2</sub> |                 | 200        |                   |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |                  | Charles and the |            | 621               |

# 46

### HOLD -- RQ/GT.

- In Minimum Mode this line carries the HOLD input signal from another master requesting a local bus.

- The DMA Controller issues the HOLD signal to request for the system bus.

- In response 8086 completes the current bus cycle and releases the system bus.

- In Maximum Mode it carries the bi-directional RQ<sub>0</sub>/GT<sub>0</sub> (Request/Grant) signal.

- The external bus master (8089 or 8087) sends an active low pulse to request for the control over the system bus.

- In response the 8086 completes the current bus cycle, releases the system bus and sends an active low Grant pulse on the same line to the external bus controller.

- 8086 gets back the system bus only after external bus master sends an active low release pulse on the same line.

#### HLDA -- RQ1/GT1

- In Minimum Mode, this line carries the HLDA signal.

- This signal is issued by 8086 after releasing the system bus.

- In Maximum Mode it functions as  $RQ_1/GT_1$  which is the same as  $RQ_0/GT_0$ ; but is of lower priority

#### WR --- LOCK

- In Minimum Mode this line carries the WR signal indicates a write operation when this pin is Low.

- It is used with M/IO to write to Memory or IO Device.

- In Maximum mode it functions as the LOCK output line.

- When 8086 executes an instruction with the LOCK prefix this signal is active (i.e. low) remains active till next instruction, indicating the external bus master cannot take control of the system bus.

### DEN --- S.

- In Minimum Mode it carries the DEN signal and is used to enable the Data transceivers (bidirectional buffer IC 8286).

- In Maximum Mode it carries the  $S_0$  signal.  $S_0$  is a status signal given to 8288.

- In Maximum Mode, Bus Controller (IC 8288) generates the DEN signal for 8286.

### $DT/R \longrightarrow S_1$

- In Minimum Mode it carries the DT/R signal indicating Data Transmit or Receive.

- This signal goes low for a read operation and high for a write operation.

- In Maximum Mode it carries the  $\overline{S_1}$  signal.  $\overline{S_1}$  is a status signal given to 8288.

- In Maximum Mode, Bus controller issues the DT/R signal to 8286...

#### M/IO --- S.

- In Minimum Mode it carries the M/IO signal, to distinguish between Memory and IO access.

- In Maximum Mode it carries the  $S_2$  signal.  $S_2$  is a status signal given to 8288.

- In Maximum Mode  $\overline{S_2}$ ,  $\overline{S_1}$  and  $\overline{S_0}$  are used to generate the appropriate control signal.

| S2 | $\overline{S}_1$ | So  | Machine cycle         |

|----|------------------|-----|-----------------------|

| 0  | 0                | Ó   | Interrupt Acknowledge |

| 0  | 0                | 1   | Read I /O Port        |

| 0  | 1                | 0   | Write I / O Port      |

| 0  | 1                | 1   | Halt                  |

| 1  | 0                | . 0 | Code Access           |

| 1  | 0                | 1   | Read Memory           |

| 1  | 1                | 0   | Write Memory          |

| 1  | 1                | 1   | Passive               |

### ALE --- QSo

- In Minimum Mode it carries the ALE signal, which is used to demultiple

- In Maximum Mode it carries the QSo signal.

- It is used with QS1 to indicate the Instruction Queue Status.

- It is used with 42.

In Maximum Mode, Bus Controller 8288 issues the ALE signal. (to 14)

#### INTA --- QS1

- In Minimum Mode it carries the INTA signal.

- It is issued in response to an interrupt on the INTR line.

- It is used to read the vector number form the interrupting device.

- In Maximum Mode it carries the QS1 signal.

- In Maximum Mode, Bus Controller issues the INTA signal. (to 8086)

| QS <sub>1</sub> | QS, | Queue Status                    |

|-----------------|-----|---------------------------------|

| 0               | 0   | No Operation                    |

| 0               | 1   | First byte of Opcode from queue |

| 1               | 0   | Empty the Queue                 |

| 1               | 1   | Subsequent byte from queue      |

#### 11.7 **Intel 8088 Microprocessor**

The Intel 8088 processor is very similar to 8086 in many aspects. In this section will discuss the pin diagram internal architecture and features of 8088.

The internal architecture of 8086 is similar to that of 8086 but the external data of 8088 but the 8 of 8088 is only 8 bit  $(D_7 - D_0)$ .

## Internal Architecture of 8088

The internal architecture of 8088 is as shown in Fig. 11.7.1. It shows that except the shows the shows that except the shows the s Queue every thing else is exactly same as that in 8086.

The queue in 8088 is of 4 byte length instead of being 6 byte long like 8086.