# 2.4 Pin Functions

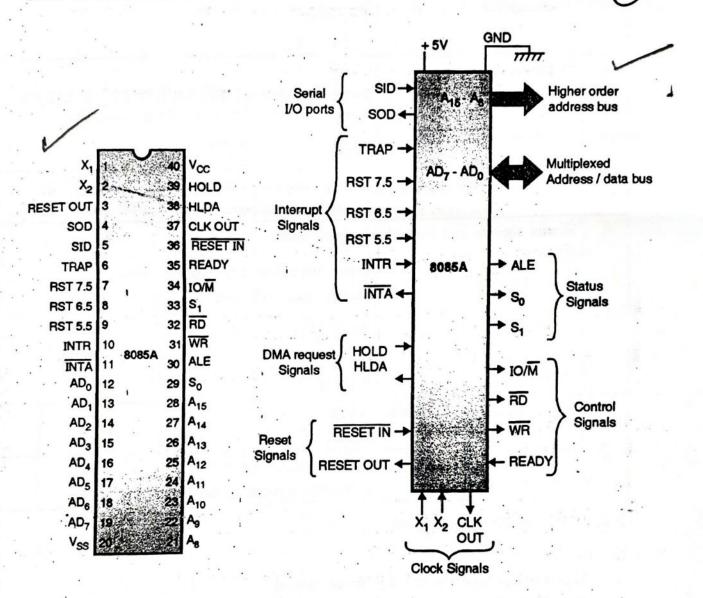

Fig. 2.4.1: Pin diagram of 8085

こいのできるというでき

Fig. 2.4.2: Groups of 8085 signals

The 8085A is an 8 bit general purpose microprocessor having 40 pins and works on single power supply. Fig. 2.4.1 shows the pin diagram of 8085A. To study the pin diagram we group the signals as shown in Fig. 2.4.2. They are as follows:

| Sr.<br>No. | Signals              | e eggener en væge<br>egne vægestadt sæ   | Pin | S |

|------------|----------------------|------------------------------------------|-----|---|

| 1.         | Power supply signals | V <sub>CC</sub><br>V <sub>SS</sub>       |     |   |

| 2.         | Clock signals        | X <sub>1</sub> X <sub>2</sub><br>CLK OUT |     |   |

| Sr.      | 2-12 8085 Architecture             |                                                                                                 |  |  |  |

|----------|------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|

| No.      | Signals                            | Pins                                                                                            |  |  |  |

| 3.       | Reset signals                      |                                                                                                 |  |  |  |

|          |                                    | RESETIN<br>RESET OUT                                                                            |  |  |  |

| 4.       | Interrupt signals                  | TRAP                                                                                            |  |  |  |

|          |                                    | Restart interrupts (RST 7.5, RST 6.5 and RST 5.5) INTR                                          |  |  |  |

| 5.       | Add                                | INTA                                                                                            |  |  |  |

| <u> </u> | Address bus and data bus           | Address bus (A <sub>8</sub> – A <sub>16</sub> )                                                 |  |  |  |

| 6.       | Status signals and control signals | Multiplexed address / data bus (AD <sub>0</sub> – AD <sub>7</sub> )  Address latch enable (ALE) |  |  |  |

|          | Signals .                          | Input output/memory (IO/M)                                                                      |  |  |  |

|          |                                    | Status signals (S <sub>1</sub> and S <sub>0</sub> )                                             |  |  |  |

|          |                                    | Read (RD)                                                                                       |  |  |  |

|          |                                    | Write (WR)                                                                                      |  |  |  |

| 7.       | Serial input/output signals        | READY<br>HOLD                                                                                   |  |  |  |

| 8.       |                                    | HLDA                                                                                            |  |  |  |

| 0.       | DMA request signals                | SID (Serial input data) SOD (Serial output data)                                                |  |  |  |

(1

# 2.4.1 Power Supply Signals

# $V_{CC}$ and $V_{SS}$

$V_{\rm CC}$  is to be connected to + 5 V power supply.

Vss - Ground reference.

# 2.4.2 Clock Signals

#### (1) $X_1 X_2$

These are clock input signals, connected to crystal, LC or RC network. The

The X<sub>1</sub> and X<sub>2</sub> pins drive the internal clock generator circuit. Hence,

The frequency is divided by 2 and used as operating frequency. Generally the The frequency is aivided by 2 and used as operating frequency. Generally the 6.014 MHz crystal is connected to X<sub>1</sub> and X<sub>2</sub>, this is divided by 2. So the CLK OUT

### (2)

This is an output signal, used as a system clock.

The internal operating frequency is available on CLK OUT pin.

The internal operating frequency is available of the internal operating frequency is available of the purple of the for the die The internal of the peripherals as a system clock input for different and the microprocessor.

### **Reset Signals**

What happens when 8085 CPU is reset?

### RESETIN

ure

- This is an active low, input reset signal. When RESETIN = 0, it clears programmakes address, data and control lines tristated. After programmakes This is an active low, input reset signal.

Counter i.e. 0000 and makes address, data and control lines tristated. After progression register and flags are unpredictable. The instruction register counter i.e. 0000 and makes address, data unpredictable. The instruction register and flags are unpredictable. The instruction register the program counter is reset. All maskable in the program counter is reset. status of internal register and mags and register reset. All maskable internal register reset. Halt flip-flop is reset. The program counter is reset. All maskable internal register reset.

- The CPU is held in the reset condition as along as RESETIN is applied.

- After reset the microprocessor starts executing instructions from 0000 H onward

- This is an active high, output signal used to indicate that the microprocessor

- This signal is used as system reset, to reset other devices connected in system

# 2.4.4 Interrupt Signals

#### (1) TRAP

- This is an active high level and edge triggered, non maskable, vector highest priority interrupt.

- When TRAP line is active microprocessor performs internal res automatically at vector address 0024 H.

# Restart interrupts (RST 7.5, RST 6.5 and RST 5.5)

- These are active high level, triggered, vectored, maskable interrupt. cause an internal restart to be automatically inserted.

- The priorities of these are RST 7.5, RST 6.5, RST 5.5.

- When RST 7.5, RST 6.5 or RST 5.5 is active microprocessor perfe internal restart automatically at vector addresses 003C H, 0034 H, 002

#### (3) INTR

- INTR is an active high, level triggered, general purpose, non-vecti

- It has the lowest priority.

- Whenever a device requires a service it has to request service on this pirmaking it's logic "1"

- The interrupting device has to state where the interrupt service routing placed in the memory. placed in the memory.

# (4) INTA

It is an output signal.

INTA is used to indicate that the microprocessor has received an INTR interrupt.

### 2.4.5 Address Bus and Data Bus

Q. Address bus is unidirectional. Justify this statement.

### Address bus (A<sub>8</sub> - A<sub>15</sub>)

- These are output, tristate signals used as higher order 8 bits of 16 bit address.

- The address bus is always unidirectional meaning that the address is given by 8085 to select a memory or an I/O location.

- It is used to identify a memory location or a peripheral device.

### 2) Multiplexed address/data bus (AD<sub>0</sub> - AD<sub>7</sub>)

- Q. 1 Why are the ADo AD, lines multiplexed?

- Q. 2 What do you mean by multiplexed addressed data bus?

- Q. 3 What is the advantage and disadvantage of multiplexed bus?

- These are input/output, tristate signals having two set of signals. They are address and data.

- The lower order 8 bits, of 16 bit address is multiplexed or time shared with data bus.

- They are demultiplexed with the help of ALE signal. During the earlier part it is used as lower order address and in later part it is used as data bus.

- The address and data buses are multiplexed to reduce the number of pins of the chip.

### 2.4.6 Status and Control Signals

Q. What are the main control signals used by 8085? Explain their function.

## Address latch enable (ALE)

- This is an output signal, used to give information of AD<sub>0</sub> AD<sub>7</sub> contents.

- It is a positive going pulse generated during the first clock cycle of a machine cycle.

- When pulse is high it indicates that the contents of AD<sub>0</sub> AD<sub>7</sub> are address.

When it is low it indicates that the contents are data.

- The ALE signal is used to separate AD<sub>0</sub> AD<sub>7</sub> (i.e. demultiplex) to A<sub>0</sub> A<sub>7</sub> and D<sub>0</sub> D<sub>7</sub>. To do this separation an external latch is connected to AD<sub>0</sub> AD<sub>7</sub> lines and this latch is controlled by ALE signal.

#### Input output/memory (IO/M) 2)

- This is an output status signal, used to give information of operation to be performed with memory or I/O device.

- If HO/M = 0, the microprocessor is performing a memory related operation.

2-15

If  $IO/\overline{M} = 1$  the microprocessor is performing an I/O device related operation.

#### Status signals (S<sub>1</sub> and S<sub>0</sub>) 3)

- These are output status signals used to give information of operation performed by microprocessor.

- When  $S_0$  and  $S_1$  is combined with  $IO/\overline{M}$  we get status of all the machine cycles (operations) performed by 8085 as shown in Table 2.4.1.

**Table 2.4.1**

| Status Signals |       |     | Operation             | Control signals used  |  |

|----------------|-------|-----|-----------------------|-----------------------|--|

| IO/M           | $S_1$ | So  | Operation             | Control signals asso  |  |

| 0              | 0     | 0   | 1. 1                  | _                     |  |

| 0              | 0     | 1   | Memory write          | WR                    |  |

| 0              | 1     | 0   | Memory read           | RD                    |  |

| 0              | 1     | _1_ | Opcode fetch          | RD                    |  |

| 1              | 0     | 0   |                       |                       |  |

| 1              | 0     | 1   | I/O write             | WR                    |  |

| 1              | 1     | . 0 | I/O read              | RD                    |  |

| 1              | 1     | 1   | Interrupt acknowledge | INTA                  |  |

| Z              | 0     | 0   | Halt                  | A 4.00                |  |

| Z              | X     | X   | Hold                  | ].                    |  |

| Z              | X     | X   | Reset                 | Inspecified condition |  |

### Read (RD)

- This is an active low signal.

- It is an output control signal that is used to read data from the selected memory location or an I/O location via the data bus.

- A low on this pin indicated that a operation performed is a read operation.

#### Write (WR) 5)

- This is an active low signal.

- It is an output control signal used to write data to selected memory location or an I/O location via data bus.

A low on this pin indicated that a operation performed is a write operation.

#### READY 6)

This is an active high input control signal.

It is used by microprocessor to detect whether a peripheral is ready for the data transfer or not. If not the processor waits till the signal goes high.

The main function of this pin is to synchronize the microprocessor 8085 with slower peripherals. i.e. the microprocessor waits till the peripheral is not ready to accept/send the data.

### 2.4.7 DMA Request Signals

### **HOLD and HLDA**

- HOLD is an active high, input signal used by other controller to request microprocessor about use of address, data and control signals.

- The Hold and HLDA signals are used for Direct Memory access (DMA).

- The DMA Controller receives a request from a device and in turn issues the HOLD signal to the microprocessor.

- The processor releases the system bus and then acknowledges the HOLD signal with HLDA signal. The DMA transfer thus begins.

- The DMA controller will use the buses. On completion of work will disable HOLD signal. Because of this microprocessor will also make HLDA low. The microprocessor takes control of buses half clock cycle after HLDA goes low.

### 2.4.8 Serial I/O Signals

What is the use of SID and SOD pins of 8085? Q.

#### SID (Serial input data) (1)

- This is an active high, serial input port pin, used to accept serial 1-bit data under software control.

- When a RIM instruction is executed the SID pin data is loaded in bit D7 of accumulator.

#### SOD (Serial output data) (2)

- This is an active high, serial output port pin, used to transfer serial 1-bit data under software control.

- When a SIM instruction is executed the SOD pin is set or reset depending on D7 and D6 bits of accumulator.

#### Address, Data and Control Buses 2.5

- What are the types of buses? Discuss 8085 microprocessor system buses.

- A set of pins, wires or signals having common function is called as bus.

- A bus is a bundle of wires that are grouped together to serve a single purpose in the serve are three sets of communication lines that are are that are and control bus and control bus are A bus is a bundle of wires that are grouped and communication lines that are sold and control bus. The three sets of communication lines that are into the address bus, the data bus and control bus. The three calls are the sold 8085 microprocessor there are three sees of the state of the sees of the state of the sees of the sees

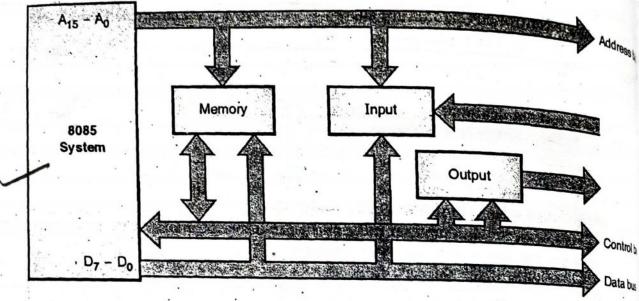

- Fig. 2.5.1 shows the 8085 bus structure.

Fig. 2.5.1: The 8085 bus structure

### **Address Bus**

- The bus over which the microprocessor sends out the address of a memory logor I/O location is called as the address bus.

- The address bus carries the address of the memory or I/O location to be real written from.

- In 8085 the address bus is 16-bit  $(A_0 A_{15})$ . So the microprocessor can be us access 16 bit address and is capable of addressing 216 = 65536 i.e. 64 K me locations.

- The address bus is unidirectional i.e. bits flow only in one direction from microprocessor unit to memory and I/O devices.

- The address bus is also used to send the port address on the address bus. Whe microprocessor reads data from or writes data to a port, it sends the port addre on the address bus.

# 2.5.2 Data Bus

- The data bus of 8085 consists of 8 parallel lines  $D_0 D_7$ .

- The data bus is a bi-directional bus. This means the data can be transferred CPU to memory or 1/O.1. CPU to memory or I/O locations and viceversa.

- The number of data lines used in the data bus is equal to the size of data word written or read written or read.

- The data bus also connects the I/O ports and microprocessor. So the micropro can write data to or read data from the memory or the I/O ports.

### 2.5.3 Control Bus

- The 8085 microprocessor uses the control bus to provide the timing signals.

- The microprocessor sends signals on the control bus to enable the outputs of addressed memory devices or I/O port devices.

- Some of the control bus signals are follows:

- (1) Memory read.

- (2) Memory write.

- (3) I/O read.

- (4) I/O write.

- These signals are used to identify a device type with which the microprocessor intends to communicate.

### 2.6 Supporting Circuits

The supporting circuits include the circuits like clock circuit, reset circuit, circuitry required for the generation of control circuits, etc.

### 2.6.1 Oscillator Circuit

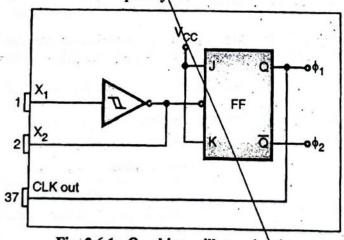

8085 provides ON CHIP OSCILLATOR. Refer Fig. 2.6.1 which shows the internal block diagram of the on chip clock generator.

• It requires tuned circuit e.g. LC, RC, crystal or an external clock source in order to generate clock.

The JK flipflop divides the frequency by 2. Hence the operating frequency of 8085 is always half of the oscillator frequency.

Fig. 2.6.1: On chip oscillator circuit

### Crystal Circuit:

- Fig. 2.6.2 shows crystal interfaced to pin no. 1 and 2. Crystal should be used, when we want stable frequency. Normally, body of crystal is grounded; this avoids external noise interference. Capacitor C<sub>1</sub> / C<sub>2</sub>; in the range of 10 20 pF; is suggested by manufacturer for start up purpose.

- In industry, people use quartz crystal ONLY for clock generation. Crystal determines frequency of oscillation.