$$\Delta t = \frac{n}{f}$$

where  $f = \operatorname{clock}$  frequency in MHz

n = number of stages

$\Delta t = \text{time delay in } \mu s$

e.g. 4-bit register having clock frequency of 2 MHz, calculate the time delay The time delay is given as

$$\Delta t = \frac{n}{f} = \frac{4}{2}$$

$$\Delta t = 2\mu s$$

#### 4.31 COUNTER

Counter is special sequential device which is used to count the clock pulses A counter have number of binary state which progress in defined fixed sequential manner.

Or

A counter is an sequential machine that is constructed with the help of flip flop and it changes its state according to the state diagram.

A counter is basically a register that is capable of counting the number of clock pulses that are available at its clock input.

The counting of counter may be ascending, descending or in any manner defined by the designer.

### For example:

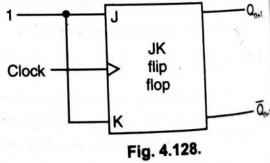

A single J-K flip-flop can acts as an counter which counts two states as shown in below diagram.

When positive edge of clock is arrived then the J-K flip-flop changes its state from 0 to 1 or 1 to 0.

Let us assume initially the flip-flop is in reset condition i.e.,  $Q_{n+1} = 0$  and we apply the input J = K = 1 hence the output is given as

$$Q_{n+1} = \bar{Q}_n$$

where

$$Q_{n+1} = \text{Next state}$$

$$Q_n = \text{Present state}$$

Sequential Logic

State D

State Arrov

changed Cou

> (i), ] (ii)

(iii)

(iv)

4.31.1 Cor

is equi Accord

(i) as sho

ic and Design

time delay.

k pulses. fined fixed

help of flip.

number of

ny manner

states as

Q<sub>n+1</sub>

Q<sub>n+1</sub>

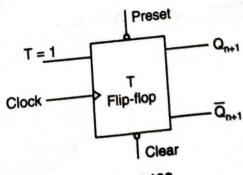

Fig. 4.129. Waveform of 1 bit counter

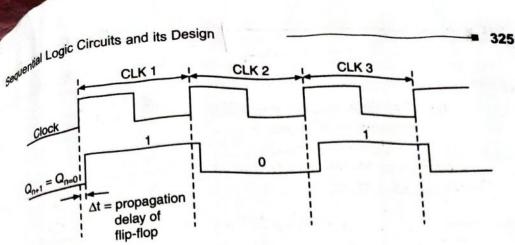

State Diagram: For single bit counter

| Truth Table |        |                    |  |  |  |  |

|-------------|--------|--------------------|--|--|--|--|

| Clock       | Output | $(Q_{n+1})$        |  |  |  |  |

| 1           | 1      |                    |  |  |  |  |

| 1           | 0      |                    |  |  |  |  |

| 1           | 1 1    | repeating sequence |  |  |  |  |

FIG. 4.130.

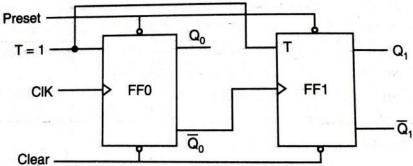

State diagram consist of circle which contains the binary value.

Arrows in state diagram show the progress sequence of the counter. State is changed on arrival of clock pulse. For each clock pulse one state is changed.

Counter can be classified on the basis of following factors.

- (i) Number of output bits or Number of flip-flop.

- (ii) Number of states or modulus counter.

- (iii) Single mode and multimode counter.

- (iii) Synchronous and Asynchronous counter.

# 4.31.1. Number of Output Bits or Number of Flip-Flop

Counters can be classified on the basis of flip-flop used. One flip-flop output is equivalent to one bit of the counter. So, it is also known as binary counters. According to this criteria the flip-flop are

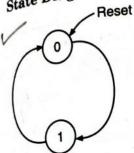

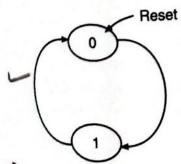

(i) Single bit Binary Counter: Single bit counter consist of two state 0, 1 as shown below in state diagram.

Fig. 4.131. State diagram of 1 bit counter

Fig. 4.132.

Fig. 4.133.

**Truth Table**

| Clock | Output $(Q_{n+1})$     |

|-------|------------------------|

| 1     | 1                      |

| 1 1   | 0)                     |

| 1     | 1 / repeating sequence |

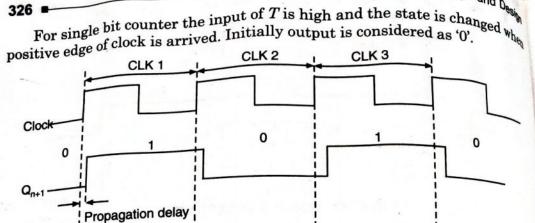

(ii) 2-bit Counter: As the name suggested two bit counter consist of two flip-flop arranged in given below manner.

Fig. 4.134. 2-bit Ripple/Asynchronous Counter

2-bit counter shown (Ripple) in above figure is an asynchronous counter in which all flip-flop are not Synchronized (means clock is not common to all flip flops).

Preset and clear inputs are used to set the output of counter i.e., initialization to "0 0" or to "11" output. The input T of the flip-flop is always connected to high logic (means '1').

State Diagram

326

of T flip-flop

Fig. 4.135.

Sequential Logic C The four pos

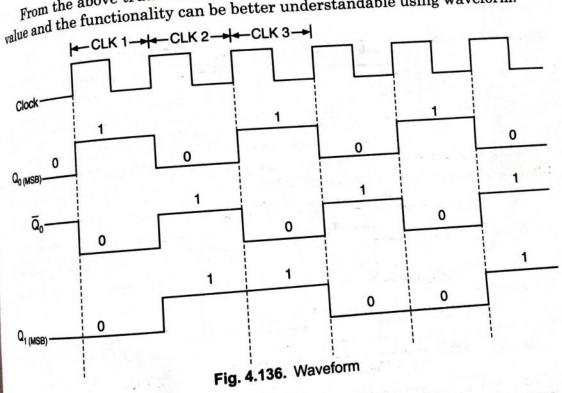

> From the value and the

> > Clock

Q<sub>0</sub> (MSB)

Qo.

Q<sub>1 (MSB)</sub>

#### Working

The we have

Wh positive

The edge o unders

(ii figure 4.

5.

Sequential Logic Circuits and its Design The four possible state of the 2 bit counter is shown in figure.

| ul P        | Truth Table          |                      |  |  |

|-------------|----------------------|----------------------|--|--|

| 1 -wise     | Output               |                      |  |  |

| Clock pulse | Q <sub>1</sub> (MSB) | Q <sub>0</sub> (LSB) |  |  |

| -           | 0                    | 0                    |  |  |

| 1.          | 0                    | 1                    |  |  |

| 2.          | 1                    | 0                    |  |  |

| 3.          | 1                    | 1                    |  |  |

repeatition/ recycle

From the above truth table it is cleared that 2 bit counter can counts four value and the functionality can be better understandable using waveform.

The working of 2 bit Asynchronous counter can be easily understandable if Working we have knowledge about the working of T-flip-flop.

When input T=1 then output  $Q_{n+1}=\bar{Q}_n$  i.e., Toggle hence on arrival of Positive edge of clock pulse the output is just opposite of previous output.

The output  $ar{Q}_0$  is feeded to the clock input of flip-flop 1 hence when positive edge of  $ar{Q}_0$  is arrived then FF1 changes its state which can be better understandable from waveform figure.

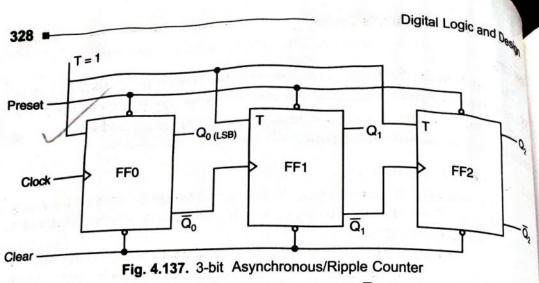

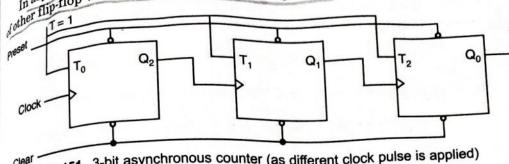

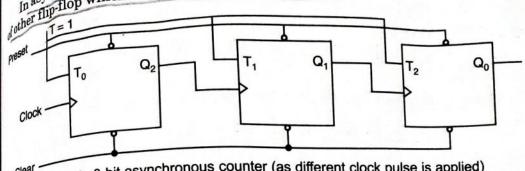

(iii) 3-bit Counter: 3 bit counter consist of 3 flip-flop as shown in below tre. figure.

two

esign vhen

nter ll flip

ation high

Clock pulse is applied to FFO and the output,  $\bar{Q}_0$  of the FFO is feeded to clock of FF-1 and similarly the output,  $\bar{Q}_0$  of the FF-1 is feeded to clock of FF-2.

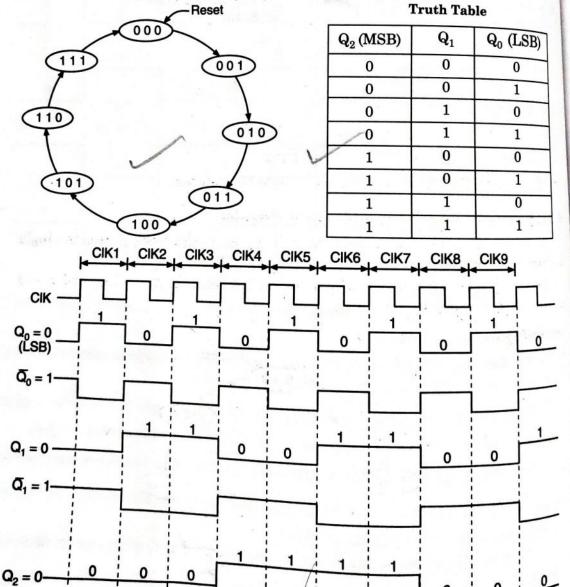

State Diagram

Fig. 4.138. Waveform of 3 bit asynchronous counter

Sequential Logic Circui

Working

The output of th FF1 calculate its or the FF2 calculates understand from w

4.31.2. Modulu

Counter can a counter consist of possible states in Modulus cour

design modulus of an Synchronou denotes '5' states

(i) Modulus & 1) and only sin

Hence mo

4.31.3. Sing

A counter manner i.e., a

For exam recycle again

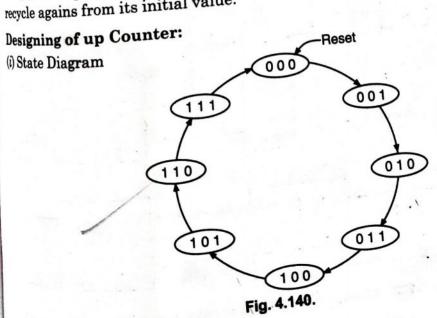

Designing of (i) State Dia

Q,

d Design

eded to FF-2.

SB)

Carcuits and its Design The output of the FF0, i.e.,  $\bar{Q}_0$  is feeded to the clock input of the FF1 hence the output when positive edge of output  $\bar{Q}_0$  is The output when positive edge of output  $\bar{Q}_0$  is arrived. Similarly  $\bar{Q}_0$  calculates its output when positive edge of  $\bar{Q}_1$  is arrived. euge of output  $Q_0$  is arrived. Similarly  $\overline{Q}_0$  is arrived which can be the  $\overline{Q}_1$  is arrived which can be the  $\overline{Q}_1$  is arrived which can be the FFF when perstand from waveform diagram.

Modulus Counter 1.2. Counter can also be classified on the basis of number of states. Modulus-2 Counter can also so the passes of number of states. Modulus-2 counter consist of two possible state, similarly modulus-4 counter consist of 4 counter consis

possible states in an counter. Modulus counter may be synchronouses or asynchronous. Generally for Modulus counter designer uses synchronous technique because design modulus counter is easier than asynchronous counter is easier than asynchronous design mountains counter is easier than asynchronous counter. e.g., MOD-5 fan Synchronous i.e., from 0 to 4 (000, 001, 010, 011, 100) of an Syllicates i.e., from 0 to 4 (000, 001, 010, 011, 100).

(i) Modulus-2 Counter: Modulus-2 counter consist of only two state (i.e., 0 (1) model and only single flip-flop is enough to design mod-2 counter.

Hence mod-2 counter is similar to single bit counter.

# 4.31.3. Single Mode and Multimode Counter

A counter is said to be single mode if it counts the clock pulses in single manner i.e., ascending order or in descending order.

For example: UP counter which counts its value in ascending order and recycle agains from its initial value.

By using state diagram we construct the state variable assignment table

shown below.

wn below. In up counter the counter counts in ascending order of decimal number;

| 1, 2,            | 3, 4      |       | ← Filled using Excitation |       |       |       |                  | on        |

|------------------|-----------|-------|---------------------------|-------|-------|-------|------------------|-----------|

|                  |           |       | Next State                |       |       | 2     | $\overline{D_1}$ | Ï         |

| Pre              | esent Sta | te    | $\overline{Q_2}$          | $Q_1$ | $Q_0$ | (MSB) |                  | 10        |

| $\overline{Q_2}$ | $Q_1$     | $Q_0$ | $\frac{\mathbf{q}_2}{0}$  | 0     | 1 0   | 0     | 0                | 1         |

| 0                | 0         | 0 0   |                           | 1     | 02    | 0     | 1                | 1         |

| 0                | 0         | 1 1   | $\frac{0}{0}$             | 1     | 13    | 0     | 1                | +         |

| 0                | 1         | 0 2   |                           | 0     | 0 4   | 1     | 0                | $\dagger$ |

| 0                | 1         | 1 3   |                           | 0     | 15    | 1     | 0                | +         |

| 1                | 0         | 0 4   | 1                         | 1     | 2.0   | 1     | 1                | +         |

| 1                | 0         | 15    | 1                         | 1     | 17    | 1     | 1                | +         |

| 1                | 1         | 06    | 1                         | 1     | 1 /   |       |                  | +         |

| 1                | 1         | 17    | 0                         | 0     | 0 0   | . 0   | 0                |           |

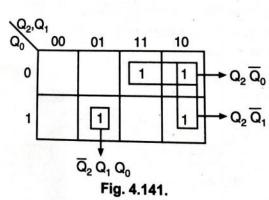

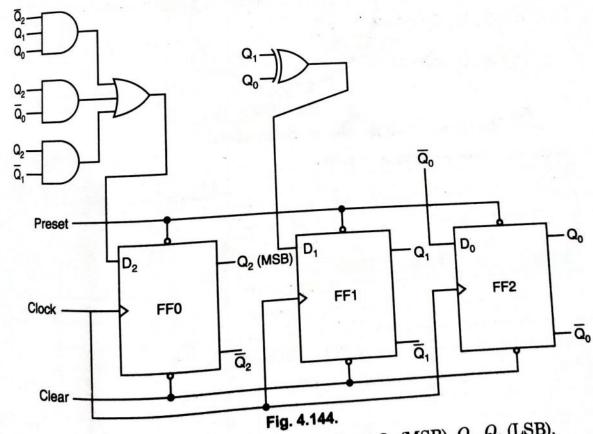

The flip-flop is selected for construction of 3 bit up counter is D flip-flop. Now use solve the equation of  $D_2$ ,  $D_1$ ,  $D_0$  with the help of k-map and implement using DFF.

$$D_2(Q_2, Q_1, Q_0) = \Sigma m (3, 4, 5, 6)$$

[for  $D_2$  the value is high at minterms 3, 4, 5 & 6]

$$D_1(Q_2, Q_1, Q_0) = \Sigma m (1, 2, 5, 6)$$

[for  $D_1$ , the vlaue is high at minterms 1, 2, 5 & 6]

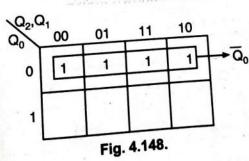

$$D_0(Q_2, Q_1, Q_0) = \Sigma m (0, 2, 4, 6)$$

[for  $D_0$ , the vlaue is high at minterms 0, 2, 4, 6]

For D<sub>2</sub>

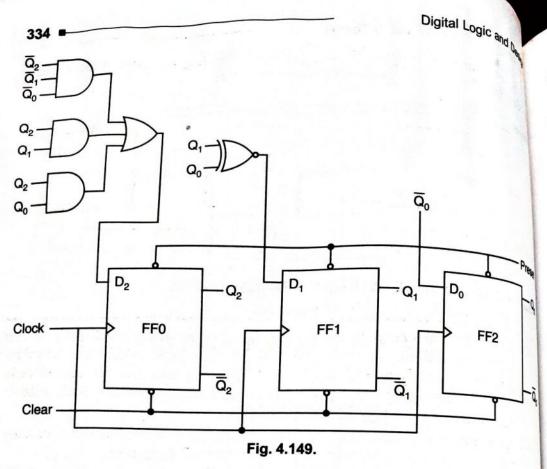

$$D_2 = \bar{Q}_2 Q_1 Q_0 + Q_2 \bar{Q}_0 + Q_2 \bar{Q}_1$$

=  $\bar{Q}_2 Q_1 Q_0 + Q_2 (\bar{Q}_0 + \bar{Q}_1)$

Sequential Logic Circuits and

FOR DI

Implement t combinational circ  $\overline{Q}_2$ . Preset

Clock

Output

Clear

ogic and Design

al number i.e.,

flip-flop. k-map and

$\frac{0}{1}$

3, 4, 5 & 6]

1, 2, 5 & 6

s 0, 2, 4, 6]

Sequential Logic Circuits and its Design

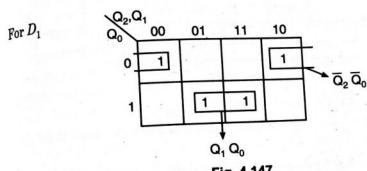

For  $D_1$   $Q_2, Q_1$   $Q_0$   $Q_1$   $Q_2, Q_1$   $Q_1$   $Q_1$   $Q_0$   $Q_1$   $Q_1$   $Q_0$   $Q_1$   $Q_1$   $Q_0$   $Q_0$   $Q_1$   $Q_0$   $Q_0$   $Q_1$   $Q_0$   $Q_$

$$D_1 = Q_1 \overline{Q}_0 + \overline{Q}_1 Q_0$$

$$= Q_1 \oplus Q_0$$

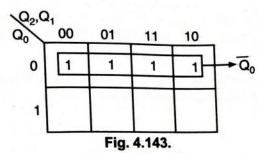

$$D_0 = \bar{Q}_0$$

Implement the equation of  $D_2$ ,  $D_1$ ,  $D_0$  with help of Flip-Flop and combinational circuits as.

Output of the 3 bit up-counter is taken from  $Q_2$  (MSB),  $Q_1$ ,  $Q_0$  (LSB).

Sequential Logic Circu Now solve the e

For  $D_2$

Note: Excitation table for flip-flop is given as:

Note: Excitation table for inputs  $Q_n$ ,  $Q_n$ , Q

| $Q_n$ (Present State) | $Q_{n+1}$ (Next State) | S<br>F | ip-Flop | Flip-Flop |     | Flip-Flor |  |

|-----------------------|------------------------|--------|---------|-----------|-----|-----------|--|

| 0                     | 0                      | 0      | ×       | 0         | ×   | 0 0       |  |

| 0                     | 1                      | 1      | 0       | 1         | . × | 1 1       |  |

| 1                     | 0                      | 0      | 1       | ×         | 1   | 1 0       |  |

| 1                     | 1                      | ×      | 0       | ×         | , 0 | 0 1       |  |

Down Counter: Down counter is also an Down Counter: Down counter is also descending counter its value in descending order only. Down counter works descending order of decimal number i.e., 7, 6, 5, 4, 3, 2, 1, 0, 7, 6...

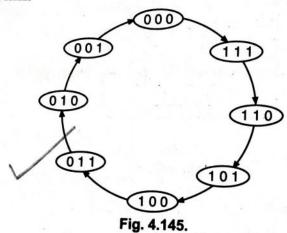

For designing the down counter first of all we make its state diagram and then state assignment table as shown below.

#### State Diagram:

State diagram of 3 bit counter is shown above.

### State variable assignment table

|                       |          |                       |                       |            | ←Usi                  | ng Exci        | tation T | able- |

|-----------------------|----------|-----------------------|-----------------------|------------|-----------------------|----------------|----------|-------|

|                       | esent St | ate                   | N                     | Next State |                       |                |          |       |

| Q <sub>2</sub><br>MSB | $Q_1$    | Q <sub>0</sub><br>LSB | Q <sub>2</sub><br>MSB | $Q_1$      | Q <sub>0</sub><br>LSB | D <sub>2</sub> | $D_1$    | $D_0$ |

| 0                     | 0        | 0                     | 1                     | 1          | LOD                   | 3              |          |       |

| 1                     | 1        | 1                     | 1                     | 1          | 1                     | 1              | 1        | 1     |

| 1                     | . 1      | 0                     | 1                     | 1          | . 0                   | 1              | 1        | 0     |

| 1                     | 0        | 1                     | 1                     | 0          | 1                     | 1              | 0        | 1     |

| 1                     | 0        | 0                     | 1                     | 0          | 0                     | 1              | 0        | 0     |

| 0                     | 1        | 1                     | 0                     | 1          | 1                     | 0              | 1        | 1     |

| 0                     | 1        | 0                     | -                     | 1          | 0                     | 0              | 1        | 0     |

| 0                     | 0        | 1                     | 0                     | 0          | 1                     | 0              | 0        | · 1   |

| A                     |          |                       | 0                     | 0          | 0                     | 0              | 0        | 0     |

For  $D_1$

For  $D_0$

Now im combination ogic and Design

its  $(Q_n, Q_{n+1})$ . Flip-Flop

0 1 0

er which can s descending

diagram and

Table-

Do

1

0 1

Logic Circuits and its Design Now solve the equation for  $D_2$ ,  $D_1$ ,  $D_0$  using k-map  $D_2$  ( $Q_2$ ,  $Q_1$ ,  $Q_2$ ) =  $\nabla$  $D_2(Q_2, Q_1, Q_0) = \Sigma_{\rm m}(0, 5, 6, 7)$

$$D_1(Q_2, Q_1, Q_0) = \sum_{m \in \{0, 3, 4, 7\}} (0, 3, 4, 7)$$

$$D_0(Q_2, Q_1, Q_0) = \Sigma_m(0, 2, 4, 6)$$

For D2  $\overline{\mathbf{Q}}_{2} \, \overline{\mathbf{Q}}_{1} \, \overline{\mathbf{Q}}_{0}$ Q2 Q1 Fig. 4.146.

$$D_2 = \ \overline{Q}_2 \ \overline{Q}_1 \ \overline{Q}_0 + Q_2 \ Q_1 + Q_2 \ Q_0$$

Fig. 4.147.

$$D_1 = Q_1 Q_0 + \bar{Q}_1 \bar{Q}_0 = Q_1 \odot Q_0$$

For  $D_0$

$$D_0 = \bar{Q}_0$$

Now implementing the equation of  $D_2$ ,  $D_1$ ,  $D_0$  using D Flip-Flop and combinational circuit.

#### **Multimode Counter**

Multimode counter are counter which works in two or more than  $two \, mode$  with the help an extra input.

For example: Up/Down counter is an multimode counter which can count in up direction as well as in down direction.

## 4.31.4 Asynchronous Counter and Synchronous Counter

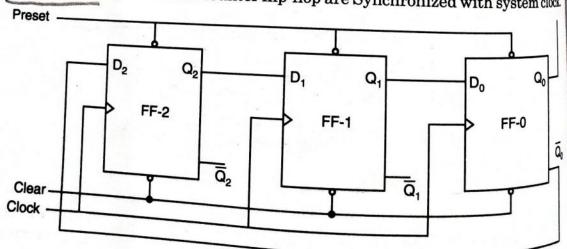

Synchronous counter is an counter in which same clock pulse is applied to all flip-flop. In synchronous counter flip-flop are Synchronized with system clock

Fig. 4.150. 3-bit synchronous counter (as same clock pulse is applied to FF<sub>0</sub>, FF<sub>1</sub> & FF<sub>2</sub>)

Synchronous Counter is an counter in which all the flip-flop are energized with same clock pulse.

Sequential Logic Circle

In asynchronous

of other flip-flop w

Preset T = 1

Clock

Fig. 4.151.

# 4.32 COMPAR

- Asynchronomy other me next flip common

- Asynchr while Sy

- Asynchi while sy

- Asynchicto Synchic

- In asymptotespresen

### Asynchrono

In asynch of other flip-f

$\overline{Q}_2$

In this output of F T inputs i.e the negative one flip for asynchro

sequential Logic Circuits and its Design In asynchronous counter the output of one flip-flop is feeded to clock input In asynction which is shown in below diagram.

L=1

Fig. 4.151. 3-bit asynchronous counter (as different clock pulse is applied)

### COMPARISON BETWEEN ASYNCHRONOUS AND SYNCHRONOUS COUNTER

- Asynchronous counter is a type of counter in which clock pulse is not common to all the flip-flops. For first flip-flop clock pulse is given and for other means 2<sup>nd</sup> flip-flop, the output of first flip-flop is acting as a clock to next flip-flop and so on while in Synchronous counter the clock pulse is common to all the flip-flops.

- Asynchronous counter (Ripple Counter) is also known as serial counter while Synchronous counter is known as parallel counter.

- Asynchronous counter (divide by N or Ripple Counter) is simpler to design while synchronous counter is difficult is to design.

- Asynchronous counter requires the least amount of hardware as compared to Synchronous Counter.

- In asynchronous counter unwanted spikes are produced which is not present in Synchronous Counter.

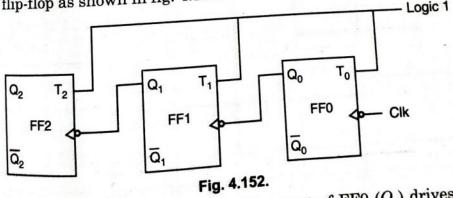

# Asynchronous Counter/Ripple Counter

In asynchronous counter, the output of one flip flop is feeded to clock input of other flip-flop as shown in fig. 4.155.

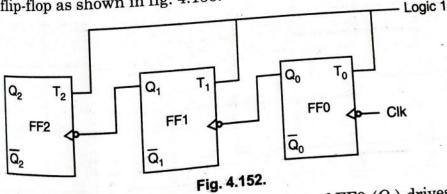

In this the Clk input drives FFO and output of FFO  $(Q_0)$  drives FF1 and Output of FF1  $(Q_1)$  drives FF2 which indicates a kind of asynchronous counter. Tinnet. Tinputs i.e.,  $T_0$ ,  $T_1$ ,  $T_2$  are connected to logic 1. Here, each flip flop toggles at the page. the negative edge of CLk pulse (as bubble is shown in clock pulse). As output of one of the negative edge of CLk pulse (as bubble is shown in clock pulse). One flip flop (F/F) drives clock input of other, hence it is called as an dsynchronous counter and as trigger moves like a ripple in water, hence it is

Preset Q FF2 ã,

than two mode

ich can counts

se is applied to n system clock.

ire energized

gapential Logic Circuits and its Design In asynchronous counter the output of one flip-flop is feeded to clock input flip-flop which is shown in below diagram. In asynction which is shown in below diagram.

Fig. 4.151. 3-bit asynchronous counter (as different clock pulse is applied)

## COMPARISON BETWEEN ASYNCHRONOUS AND SYNCHRONOUS COUNTER

- Asynchronous counter is a type of counter in which clock pulse is not common to all the flip-flops. For first flip-flop clock pulse is given and for other means 2nd flip-flop, the output of first flip-flop is acting as a clock to next flip-flop and so on while in Synchronous counter the clock pulse is common to all the flip-flops.

- Asynchronous counter (Ripple Counter) is also known as serial counter while Synchronous counter is known as parallel counter.

- Asynchronous counter (divide by N or Ripple Counter) is simpler to design while synchronous counter is difficult is to design.

- Asynchronous counter requires the least amount of hardware as compared to Synchronous Counter.

- In asynchronous counter unwanted spikes are produced which is not present in Synchronous Counter.

## Asynchronous Counter/Ripple Counter

In asynchronous counter, the output of one flip flop is feeded to clock input of other flip-flop as shown in fig. 4.155. Logic 1

In this the Clk input drives FFO and output of FFO  $(Q_0)$  drives FF1 and Output of FF1  $(Q_1)$  drives FF2 which indicates a kind of asynchronous counter. Tinputs i.e.,  $T_0$ ,  $T_1$ ,  $T_2$  are connected to logic 1. Here, each flip flop toggles at the negative shown in clock pulse). As output of the negative edge of CLk pulse (as bubble is shown in clock pulse). As output of the firm  $\pi$ One flip flop (F/F) drives clock input of other, hence it is called as an asymptotic street of the s delynchronous counter and as trigger moves like a ripple in water, hence it is

Preset Q F<sub>2</sub> Q,

n two mode

can counts

s applied to stem clock.

Q<sub>o</sub> F-0 Q0

e energized

called as a ripple counter when  $Q_0$  takes a transition from  $1 \to 0$ , then called as a ripple counter when  $Q_0$  takes a transition from  $1 \to 0$ , then  $Q_0$  takes a transition from  $Q_$ called as a ripple counter when Q1 takes a transition from 1 trigger FF1 means FF1 toggles and when Q1 takes a transition from 1 trigger FF2 means FF2 toggles. Hence overall propagation del trigger FF1 means FF1 toggles. Hence overall propagation delays of FF0, FF1, FF2 it can trigger FF2 means 1 time is equal to sum of individual propagation delays of FF0, FF1, FF2  $(P.D)_{Ripple \text{ counter}} = (PD)_{FF0} + (PD)_{FF1} + (PD)_{FF2}$

Operation:

The 3-bit ripple counter truth table is given as below

|   | Clk                             | $Q_2$            | $Q_1$                                       | $Q_0$  |

|---|---------------------------------|------------------|---------------------------------------------|--------|

|   | 0                               | 0                | 0                                           | 0      |

|   | 1                               | 0                | 0                                           | 1      |

|   |                                 |                  | 1                                           | 0      |

|   | 2<br>3<br>4<br>5<br>6<br>7<br>8 | 0<br>0<br>1<br>1 | 1_                                          | 1      |

|   | 4                               | 1                | $\begin{bmatrix} 1 \\ 0 \\ 0 \end{bmatrix}$ | 1<br>0 |

|   | 5                               | 1                | 0                                           | 1      |

|   | 6                               | 1                | 1                                           | 0      |

| 1 | 7.                              | 1                | 1_                                          | 1      |

|   | 8                               | 0                | 0                                           | 0      |

Initially all F/Fs are cleared hence  $Q_2 = Q_1 = Q_0 = 0$ . FF0 toggles at every clock pulses on negative transition of clock. At 1st clock pulse  $0 \rightarrow 1$  transition Q0 cannot trigger  $Q_1$  as it's a positive change hence  $Q_1 = 0$ .

Similarly  $0 \to 0$  state of  $Q_1$  cannot trigger  $Q_2$ . Hence  $Q_2 = 0$ .

In this way counter will count from 000 - 111.

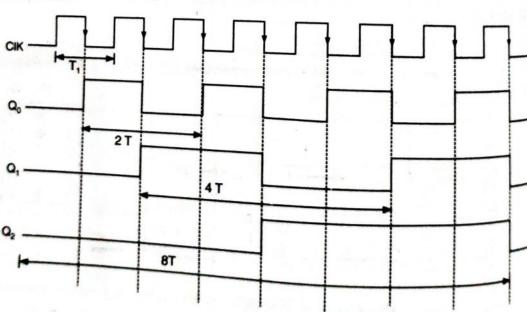

#### Waveform

Fig. 4.153.

This counter can be utilized as a frequency counter. As time period is becoming double, hence frequency is becoming half i.e.

$$Q_0 = \frac{1}{2} \left( \text{Clk f} \right)$$

Sequential Logic C

So by using

it can count fro PROBLEM D

(1) MoD 3 (4) MoD 7

Solution : It J = K = 1 or by

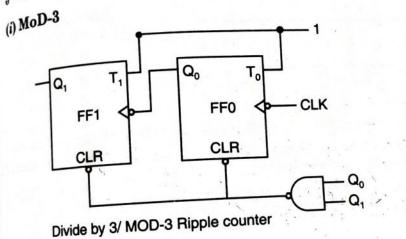

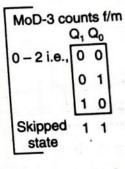

(i) MoD-3

Divid

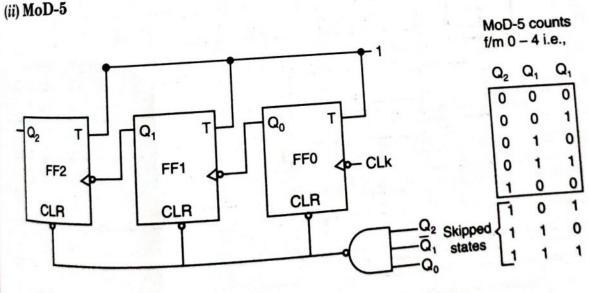

(ii) MoD-5

FF2 CLR lic and Design , then it can  $n \rightarrow 0$  then delay (PD)

Sequential Logic Circuits and its Design

$$Q_1 = \frac{1}{4} \left( \text{Clk f} \right)$$

$$Q_2 = \frac{1}{8} (\operatorname{Clk} f)$$

So by using three flip flops, we can get  $2^3 = 8$  distinct/unique states. Hence  $\int_{\text{it can count from }} \left[0 - (2^3 - 1)\right] \text{ i.e., } 0 - 7 \text{ states.}$

PROBLEM Design the following asynchronous (Ripple counter)

(2) MoD 5

(1) MoD 3

(3) MoD 6

(5) MoD 9

Solution: It can be designed by specifically by J-K F/F counter. The condition of the using TF/F and T = 1Solution by using TF/F and T = 1

Divide by 5/ MoD-5 Ripple counter

es at every ansition of

half i.e.,