Digital Logic and Design

268

Here

| CLK | D | Q         |

|-----|---|-----------|

| 0   | × | No change |

| 1   | 0 | 0         |

| 1   | 1 | 1         |

Case 1:

$$D$$

– High

$$Q_n = 1 \qquad \text{in fig 4.45}$$

If

$$D = 1$$

Means

$$S=1 \quad \& \quad R=0$$

That's case of S-R Flip-Flop, Flip-Flop is said to be in set state and  $\log_{1} \log_{1} \log_{1}$ stored.

Case 2:

$$D-Low$$

$Q_n = 1$ in fig. 4.45

If

Means

$$S=0$$

&  $R=1$

That's again case of S-R Flip-Flop, Flip-Flop is said to be in Reset state and logic 0 is stored.

#### DO YOU KNOW?

D Flip-Flop is also known as Delay Flip-Flop.

#### Concluding Case 1 and Case 2

"The output Q follows input D at rising edge of clock pulse".

Truth Table:

| Positive edge Triggered clock | D | $Q_{n+1}$ | $\overline{Q_{n+1}}$ |

|-------------------------------|---|-----------|----------------------|

| <b>†</b>                      | 1 | 1         | 0                    |

|                               | 0 | 0         | 1                    |

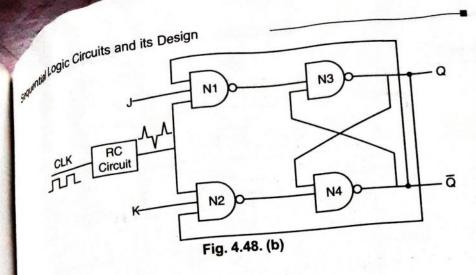

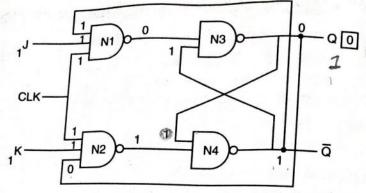

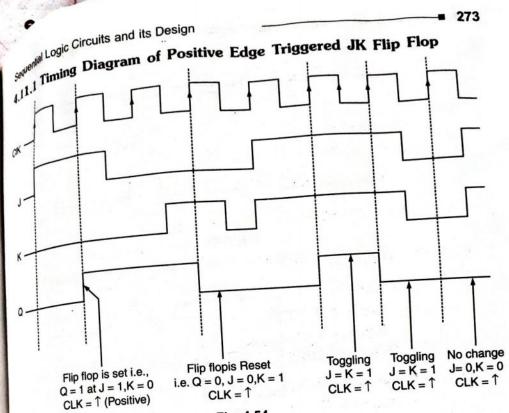

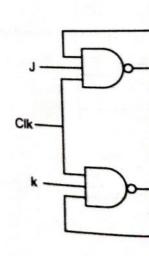

## 4.11 EDGE-TRIGGERED J-K FLIP-FLOP

J-K Flip-Flop is also identical to S-R Flip-Flop but having the advantages that, it does not have invalid state. Features -

- It's a versatile Flip-Flop

- It avoids the invalid-state condition of S-R Flip-Flop — It is most widely used Flip-Flop among all Flip-Flops.

- It is most widely used in digital system.

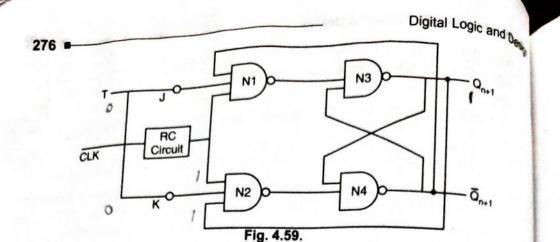

J.K Flip-Flop is derived from S-R Flip-Flop by connecting Q output back with input of  $N_2$  and simultaneously  $\overline{Q}$  output back with input of  $\overline{N_1}$

sequential Logic Circuit

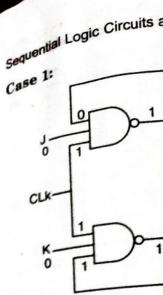

Case 1:

K-

Let's take

Ou Ou

I

Hence ou

Hence or

Hence there assumed.

OW? known as

ntages that,

output back

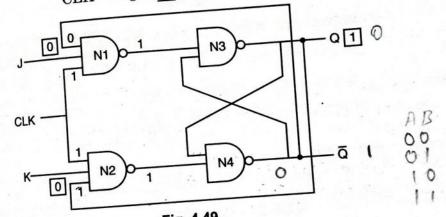

Case 1: J = 0K = 0) is shown as Clk = 1 CLK - High (\_\_\_

Fig. 4.49.

Let's take

$$Q = 1$$

$$J = 0$$

$$K = 0$$

Assumption

Output of  $N_1 = 1$  (: J = 0, CLK – High = 1,  $\overline{Q} = 0$ )

Output of  $N_2 = 1$  (: K = 0, CLK = 1, Q = 1)

Input of  $N_4 = 1 \ \& \ 1 \ ] \ \cdots \ Q$  is coupled back to Input of  $N_4$ Hence output of  $N_4 = 0$

Means  $\overline{Q} = 0$

Input of  $N_3 = 1 \& 0$   $\bigcirc$   $\bigcirc$  is coupled back to Input of  $N_3$ Hence output of  $N_3 = 1$

Means Q = 1Hence there is no change in the output. It is same as that we have initially

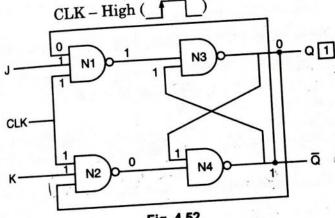

J=1K=0Q = 1CLK - High ( N3 Q 1 1 ā Fig. 4.51.

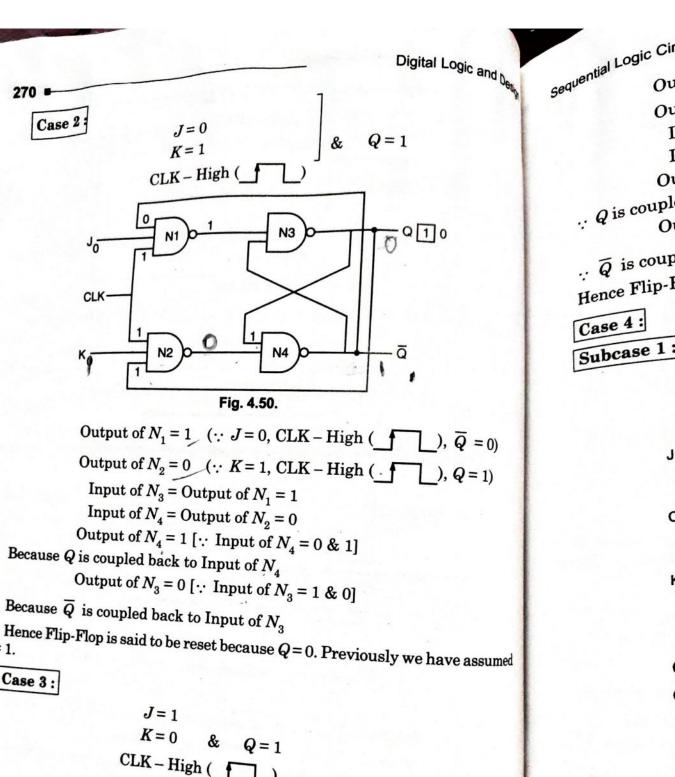

Fig. 4.50.

270

Q=1.

Case 3:

Case 2

J<sub>0</sub>

CLK-

J = 0

K=1CLK - High (

Input of  $N_3 = \text{Output of } N_1 = 1$ Input of  $N_4$  = Output of  $N_2$  = 0

Because Q is coupled back to Input of  $N_4$

Because  $\overline{Q}$  is coupled back to Input of  $N_3$

Output of  $N_4 = 1$  [: Input of  $N_4 = 0 \& 1$ ]

Output of  $N_3 = 0$  [: Input of  $N_3 = 1 & 0$ ]

&

.. Q is coupl  $\overline{Q}$  is coup Hence Flip-I Case 4:

Ou

O

Because QBecause 6

Subcase ?

ital Logic and Design

10

$$\overline{Q}$$

),  $\overline{Q}$  = 0)

$\overline{Q}$ ),  $Q$  = 1)

ve have assumed

Output of

$$N_1=1$$

( $\cdots$   $J=1$ , CLK – High ( $\bigcirc$ ),  $\overline{Q}=0$ )

Output of  $N_2=1$  ( $\cdots$   $K=0$ , CLK – High ( $\bigcirc$ ),  $Q=1$ )

Input of  $N_3 = \text{Output of } N_1 = 1$

Input of  $N_4$  = Output of  $N_2$  = 1

Output of  $N_4 = 0$  [: Input of  $N_4 = 1 & 1$ ]

Qis coupled back to Input of N<sub>4</sub> Output of  $N_3 = 1$  [: Input of  $N_3 = 1 & 0$ ]

.  $\hat{Q}$  is coupled back to Input of  $N_3$ Hence Flip-Flop is said to be set  $\therefore Q = 1$ .

Case 4: Subcase 1:

$$J=1$$

$$K=1 & Q=1$$

Fig. 4.52.

Output of

$$N_1 = 1$$

(:  $J = 1$ , CLK – High ( ),  $\overline{Q} = 0$ )

Output of

$$N_1 = 1$$

(:  $J = 1$ , CLK - High ( ),  $Q = 1$ )

Output of  $N_2 = 0$  (:  $K = 1$ , CLK - High ( ),  $Q = 1$ )

Input of  $N_3 = \text{Output of } N_1 = 1$

Input of  $N_4$  = Output of  $N_2$  = 0

Output of  $N_4 = 1$  [: Input of  $N_4 = 0 \& 1$ ]

Because Q is coupled back to Input of  $N_4$

Output of  $N_3 = 0$  [: Input of  $N_3 = 1 & 1$ ]

Because  $\overline{Q}$  is coupled back to Input of  $N_3$

Subcase 2:

$$J = 1$$

$$K = 1 & Q = 0$$

Fig. 4.53.

Output of

$$N_1=0$$

(:  $J=1$ , CLK – High (\_\_\_\_\_\_\_\_),  $\overline{Q}=1$ )

Output of  $N_2=1$  (:  $K=1$ , CLK – High (\_\_\_\_\_\_\_),  $Q=0$ )

Input of  $N_3=0$  Output of  $N_1=0$

Input of  $N_4=0$  Output of  $N_2=1$

Output of  $N_3=1$  [: Input of  $N_3=0$  & 1]

$\because \overline{Q}$  is coupled back to Input of  $N_3$

Output of

$$N_4 = 0$$

[: Input of  $N_4 = 1 \& 1$ ]

$\therefore Q$  is coupled back to Input of  $N_4$

We conclude from subcase 1 and subcase 2 that, Flip-Flop revert its state. It goes to opposite state. This condition is most commonly known as Toggle

Hence Flip-Flop is said to be set  $\therefore Q = 1$ .

#### **Truth Table**

$Q_0$  – Previous output

| CLK          | J | K | 100 march 200    |                              |

|--------------|---|---|------------------|------------------------------|

| F            |   | Λ | Q                | $\overline{Q}$               |

| <u></u>      | 0 | 0 | $Q_0$            | $\overline{Q}_0$ (No change) |

|              | 0 | 1 | 0                | 1 (Set)                      |

|              | 1 | 0 | 1                | 0 (Reset)                    |

| and level tr | 1 | 1 | $\overline{Q}_0$ | Q <sub>0</sub> (Toggle)      |

Note: If we had level triggering instead of edge triggering, then if CLK = 1, J = 1. This causes output to see a significant of edge triggering, then if LK = 1. J=1, K=1. This causes output to get complemented again and again until CLK becomes zero. This conditions at complemented again and again until caused this CLK becomes zero. This condition is undesired and hence to avoid this condition, we have taken clock pulse with edge triggering.

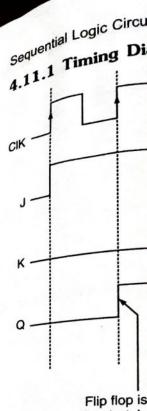

Q = 1 at J = 1CLK = 1 (

Here

## 4.12 PRESET AND

They are used to se input i.e., in order known as preset (P

These inputs a synchronism with t The signals S-R, Jthese inputs are tra of the clock pulse  $^{\text{pulse}}$ . A D type flip Digital Logic and Design

QO

$(\overline{Q}), \overline{Q} = 1$ ), Q = 0)

op revert its state. It y known as Toggle

(No change)

Set)

Reset)

(Toggle)

, then if CLK = 1, n and again until nce to avoid this

Fig. 4.54.

Here

| CLK | J   | K   | Q              |

|-----|-----|-----|----------------|

| ULK |     | ×   | No change (NC) |

| 0   | ×   | ×   | No change (NC) |

| 1   | × × | ×   | No change (NC) |

| 1   | Ô   | 0   | No change (NC) |

| ×   | 0   | · 1 | 0 (Reset)      |

| *   | 1   | 0   | 1 (Set)        |

| 1   | 1   | 1   | Toggle         |

## 4.12 PRESET AND CLEAR SIGNAL

They are used to set or reset the state of flip flop regardless of the state of clock input i.e., in order to assign the initial state of the flip flop. These inputs are known as preset (Pr) or direct set  $(S_D)$  and clear (Cr) or direct reset  $(R_D)$

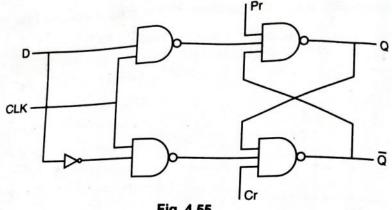

These inputs are applied at any time between clock pulses and is not Nnchronism with the clock pulse. It means that they are asynchronous signals. The signals S-R, J-K and D are synchronous signal or inputs because data on these inthese inputs are transferred to the flip flops output only on the triggering edge of the clock pulse means data are transferred synchronously with the clock pulse. A D type flip flop with preset and clear signal is shown as follows:

Fig. 4.55.

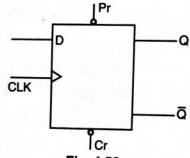

Logic symbol of D type flip flop with preset and clear is shown below:

Fig. 4.56.

They are generally active low signal. The truth table is shown as follows:

| 29  | Inputs |    | Output    | Operation        |

|-----|--------|----|-----------|------------------|

| CLK | Cr     | Pr | Q         | Performed        |

| 1   | 1      | 1  | $Q_{n+1}$ | Normal flip flop |

| 0   | 1      | 0  | 1         | Preset (Set)     |

| 0   | 0      | 1  | 0         | Clear (Reset)    |

| 0   | 0      | 0  | _         | Uncertain        |

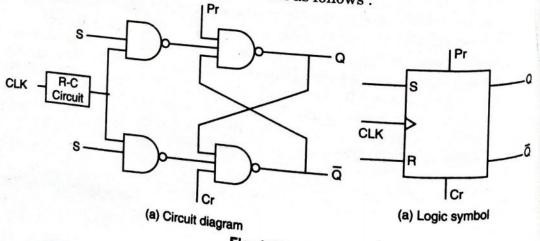

## For Clocked S-R Flip Flop

The preset and clear inputs are shown as follows:

Fig. 4.57.

Sequential Logic Circu

Here When Clk = 1, When Clk = 1, and in that cas

flop).

The Pr = Cr =are present and hi works as normal c When Clk = 0,

circuit because Cr when it is low i.e., When Clk = 0,

by the circuit. The truth tab

| The | . CC          |

|-----|---------------|

|     | Inpu          |

| CLK | Cr            |

| 1   | 1             |

| 0   | 0             |

| 0   | 1             |

|     | CLK<br>1<br>0 |

#### **Application Area**

They are use function on a mu them all at once.

### Summary

- Preset and

- Both are a

- When Pr =

- When Pr - When Pr

## 4.13 T FLIP-FLO

If we connec common connec al Logic and Design

nown below:

hown as follows:

n p flop t) set)

l Cr Logic symbol Logic Circuits and its Design

Here Clk = 1, S = 1 & R = 0, then output = 1 and Clk = 1, S = 0 & R = 1. then

When Clk = 1, S = 0 & R = 1, then output = 0 When Clk = 1, S = 0 & R = 1, then output = 0 When CIK = 1, CIK = 1, which output = 0 and in that case, the Pr = Cr = 1, works as clocked S-R flip flop (normal flip) and in that case, the Pr = Cr = 1, works as clocked S-R flip flop (normal flip)

The  $P_r = Cr = 1$ , takes the low value because inside the circuit  $\overline{P_r}$  and  $\overline{C_r}$ The reason and high on both the inputs make them low and hence, the circuit present and high on both the inputs make them low and hence, the circuit

When Clk = 0, Cr = 0 &  $P_r = 1$ , then clear operation is performed by the or present normal clocked S-R flip flop. The following  $Cr(\overline{Cr})$  is activated as they are active low signal means worked,

When Clk = 0, Cr = 1 & Pr = 0, then preset means set operation is performed shen it is low i.e., '0'. the circuit.

The truth table is given as follows:

| Inpu | PROPERTY CONTRACTOR AND ADDRESS. | ven as follows : Outputs          | Operation Performe |  |  |

|------|----------------------------------|-----------------------------------|--------------------|--|--|

| C    | Pr                               | $Q_n$                             |                    |  |  |

| Cr 1 | 1                                | $Q_{n+1}$ (Clocked S-R operation) | Normal flip flop   |  |  |

|      |                                  | 0 (Reset)                         | Clear              |  |  |

| 0    | $\frac{1}{0}$                    | 1 (set)                           | Preset             |  |  |

They are used when multiple flip flops are ganged together to perform a **Application Area** function on a multi-bit binary word and a single line is needed to set or reset them all at once.

#### Summary

- Preset and clear are asynchronous signals or inputs.

- When Pr = 0 and Cr = 1, then Preset operation is performed in the circuit. - Both are active low signal.

- When Pr = 1 and Cr = 0, then clear operation is performed in the circuit.

- When Pr = Cr = 1, then circuit perform normal flip flop operation.

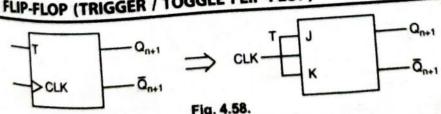

# T FLIP-FLOP (TRIGGER / TOGGLE FLIP-FLOP)

Fig. 4.58. We connect J & K inputs together in a J-K Flip-Flop, then we can label connection of J-K Flip-Flop as Tinput

Means Case 1: J=0 K=0T = 0 $Q_n = 1$

Then there is no change in the output (as seen in edge-triggered J-K Flip. Flop)  $Q_{n+1} = 1$

Means Case 2: J=1 K=1 $Q_n = 1$

Then there is reverse of state of output (as compare to previous Input) Hence  $Q_{n+1} = 0$

#### Concluding Remarks

T=1 and  $Q_n=0$  (Previous), Then  $Q_{n+1}=1$  (Present) Otherwise

If T = 1 and  $Q_n = 1$  (Previous), Then  $Q_{n+1} = 0$  (Present)

Means output will change its state from 0 to 1 or 1 to 0. This process is called toggling. That's why T Flip-Flop is also called as Toggle Flip-Flop.

| T     | Q <sub>n</sub> (Previous) | $Q_{n+1}$ (Present) |                 |

|-------|---------------------------|---------------------|-----------------|

| 0     | 0                         |                     | ange in 7       |

| 1     | 1                         |                     | ous output      |

| 1     | 0                         | 1 Comp              | lemented output |

| table | of T flin flow            | 0 of pre            | vious output .  |

DO YOU KNOW?

T Flip Flops are most

commonly used in binary

counters, because of its

i.e., Truth table of T flip flop

| T | $Q_{n+1}$        |

|---|------------------|

| 0 | $Q_n$            |

| 1 | $\overline{Q_n}$ |

# 4.14 RACE AROUND CONDITION

divide-by-2 capability. In case of level triggered JK flip flop when J=K=1, then output  $Q_{n+1}=Q_n$  i.e., output is the invert of providing the standard change i.e., output is the invert of previous output and this yields to continuous change

Sequential Logic Ci in value of  $Q_{n+1}$  f zero in a single c around condition A condition i

output is continu and 1 to 0 in a s race around cont

If  $\Delta t$  is the pr its output and T this equation mu

Where  $t_p$  is t Methods to Re There are t

follows:

(1) Use Edge (2) Flip flop

means At

pulse is condition (3) Use of M

4.15 MASTER

It's a cascade o clock is high w

Hence final effective. Henc

low.

In this way as slave.

> Mast F/F

Positiv clock

When CL (because Inver

When CL

ogic and Design

- ā<sub>n+1</sub>

ered J-K Flip.

us Input)

1 (Present)

0 (Present)

nis process is p-Flop.

ıt d output tput

10W ?

are most d in binary use of its bility.

$t Q_{n+1} = \overline{Q_n}$ nuous change

Sequential Logic Circuits and its Design from zero to one and one to  $Q_{n+1}$  from zero to one and one to  $Q_{n+1}$  single clock pulse is term as invalue of  $q_n+1$  clock pulse is term as race into in a condition.

J = K = 1 and the J = K = 1ground condition. A continuously changes from 0 to 1 is continuously clock pulse : ond 1 to 0 in a single clock pulse is called and condition.

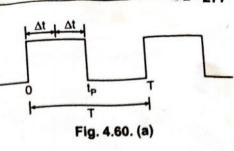

If M is the propagation delay of flip flop i.e., after  $\Delta t$  time, flip flop changes per ground condition. If M is the property of the form of one clock pulse then for race around condition are the first satisfied: this equation must satisfied:

$$\frac{0 < \Delta t < t_p - \text{Equation}}{1 + \frac{1}{2} +$$

Where  $t_p$  is time period where pulse is high.

Nethods to Remove Race-Around Condition There are three methods to remove race-around condition which are as follows:

- (1) Use Edge-Triggered flip flop.

- (2) Flip flop must follows the following equation

$$t_p < \Delta t < T$$

means  $\Delta t$  (Propagation delay) must be greater than  $t_p$  (time period when pulse is high) and lesser than T (total time period of pulse). In above condition flip flop calculate its value one time in one clock pulse.

(3) Use of Master-slave flip flop to lock the output for complete clock cycle.

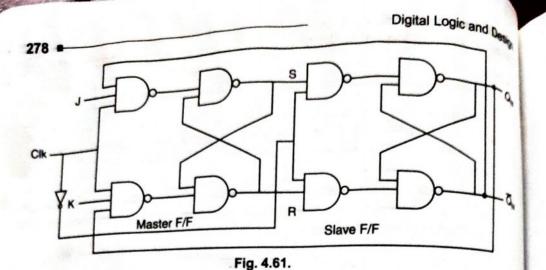

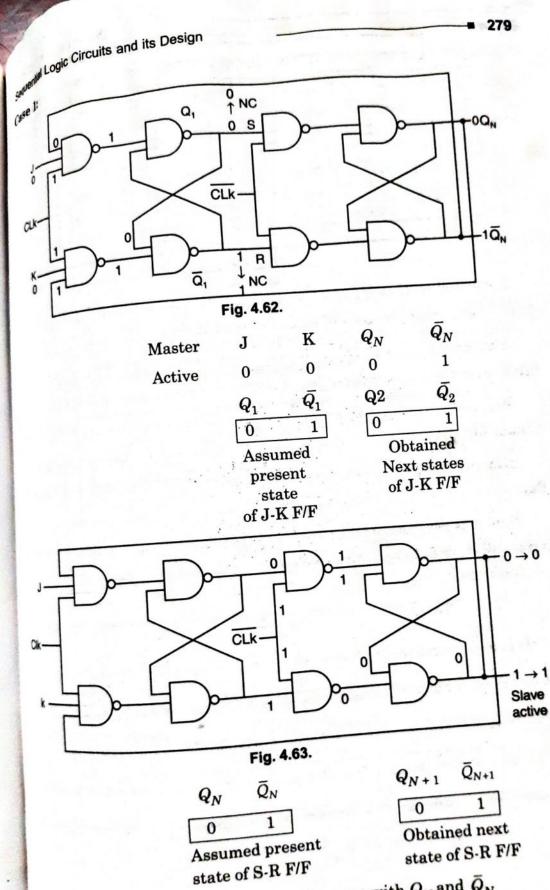

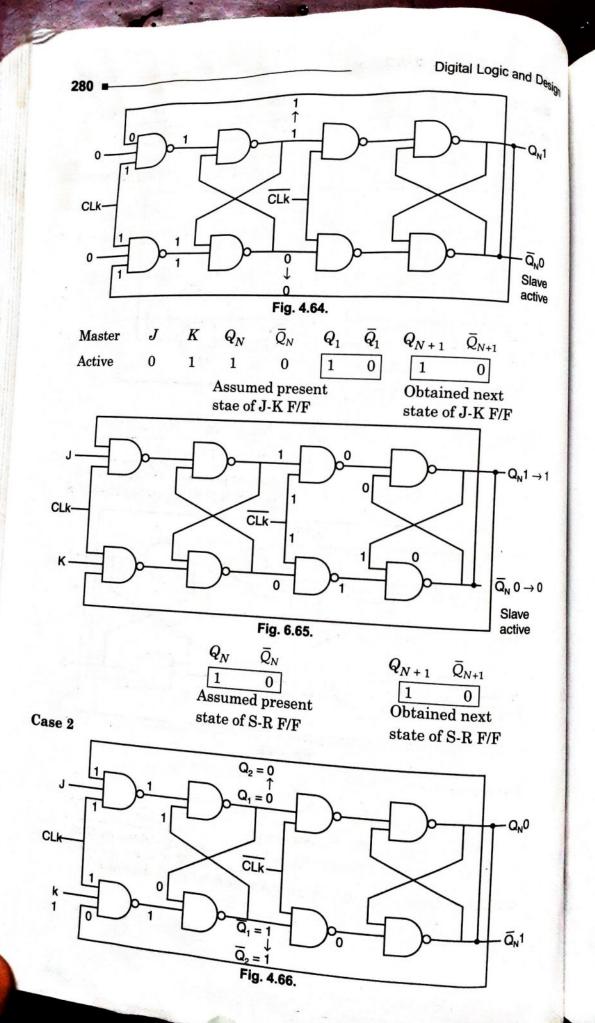

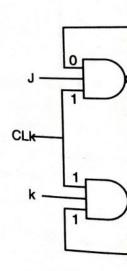

## 4.15 MASTER SLAVE J-K FLIP-FLOP

It's a cascade of two flip-flops in which first one responds to data inputs when clock is high whereas second one responds to output of first one when clock is low.

Hence final output changs only when clock is low, when data inputs are not effective. Hence race around condition gets eliminated.

In this way first flip-flop is known as master and second flip-flop is known as slave.

When CLk is High: Master will be active and slave will be deactive because Inverted CLK of master is provided to slave)

When CLK is Low: Master will be deactive and slave will be active

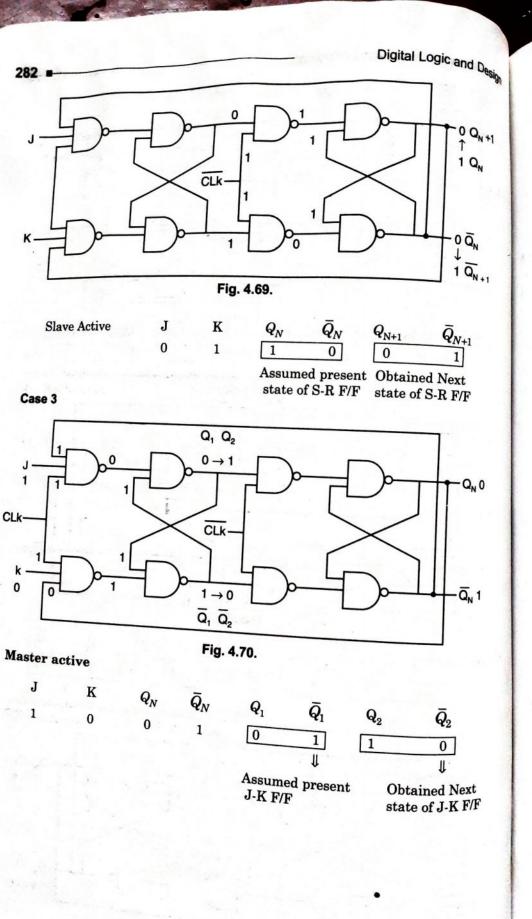

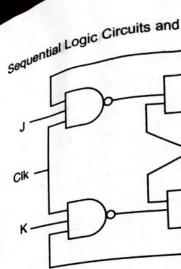

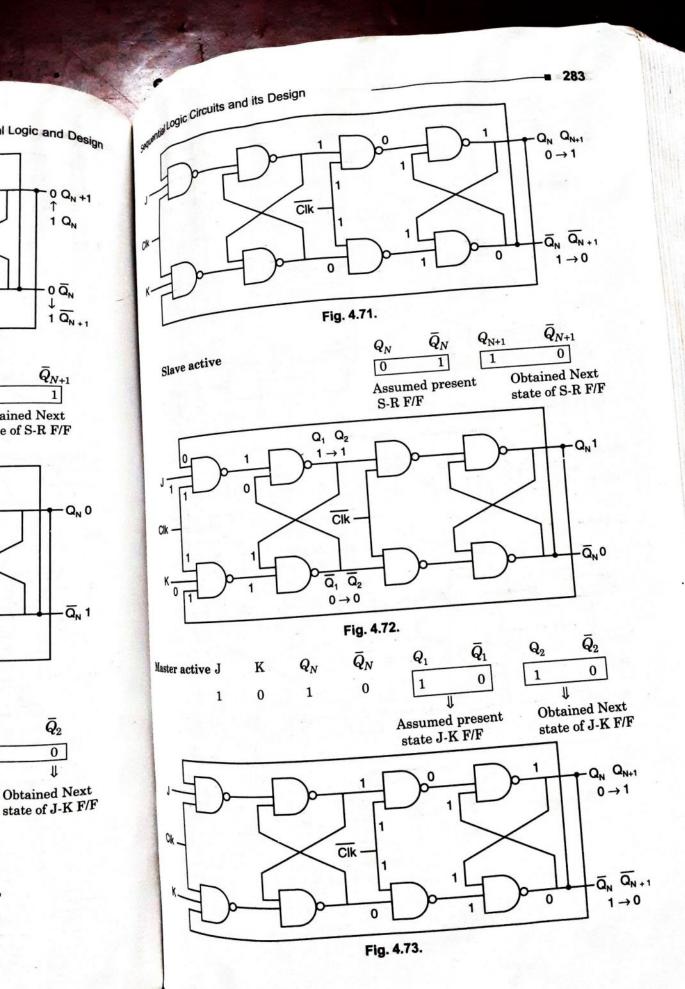

Let's assume that  $Q_N$  and  $\bar{Q}_N$  are present outputs of S-R flip-flop i.e,  $s|_{ave}$  flip-flop and most precisely of master-slave flip-flop.

Similarly  $Q_{N+1}$  and  $\overline{Q_{N+1}}$  are next state outputs of S-R flip-flop i.e., slave flip-flop and most precisely of Master-slave Flip-flop.

We also assume that  $Q_1$  and  $\overline{Q}_1$  are present state outputs of J-K flip-flop i.e, Master flip-flop.

Similarly  $Q_2$  and  $\bar{Q}_2$  are next state outputs of J-K flip-flop i.e., master flip-flop.

Now it is very important to observe that  $Q_2$  and  $\bar{Q}_2$  are driving S and R inputs of slave flip-flop respectively.

It means

$$S = Q_2$$

$$R = \bar{Q_2}$$

It is also necessary to observe that if we assume  $Q_N=0$  and  $\bar{Q}_N=1$ , then we have to automatically assume  $Q_1=0$  and  $\bar{Q}_1=1$ . Because it is not possible to achieve  $Q_N=0$  and  $\bar{Q}_N=1$  if  $S=Q_1=1$  and  $R=\bar{Q}_1=0$ .

Similarly if we assume  $Q_N=1$  and  $\bar{Q}_N=0$ . Then we have to automatically assume  $Q_1=1$  and  $\bar{Q}_1=0$  because it is not possible to achieve  $Q_N=1$  and  $\bar{Q}_N=0$  if  $S=Q_1=0$  and  $R=\bar{Q}_1=1$ .

Note: The valu

Design

Q"

e, slave

., slave

flop i.e,

er flip-

and R

, then

sible to

atically

and

Note: The values of  $Q_1$  and  $\bar{Q}_1$  must be same with  $Q_N$  and  $\bar{Q}_N$

Sequential Logic Circuits

Master J

active 0

Slave active

Master active

J

0

ogic and Design

Q<sub>N</sub>1

$\overline{Q}_{N}0$

Slave

active

$Q_N 1 \rightarrow 1$

$\overline{Q}_N 0 \to 0$ Slave

active

Q<sub>N</sub>0

Q<sub>N</sub>1

N+1

0 next

R F/F

N+1

0

next

K F/F

Slave active

Master active J K

1 0

0 ned Next of S-R F/F 285

Q<sub>N</sub> 1

Q, O

$ar{Q}_2$

**Obtained Next**

state of J-K F/F

U

Obtained Next

state of S-R F/F

1

QN QN+1

1 → 0

QN QN+1  $0 \rightarrow 1$

$\mathbf{Q}_2$

0

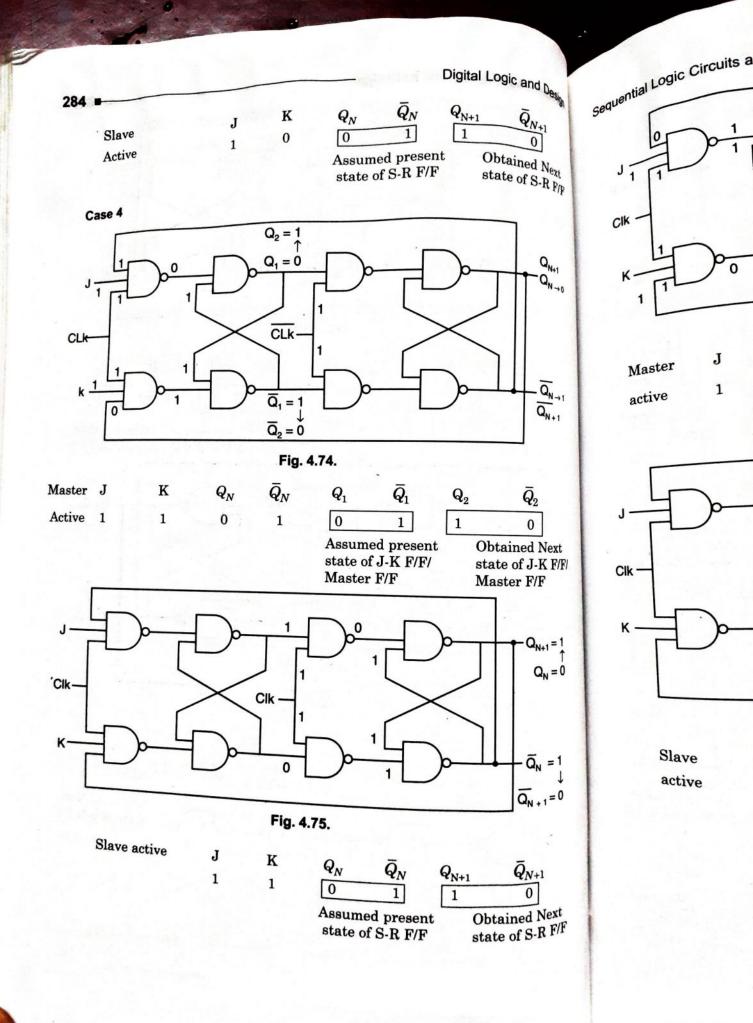

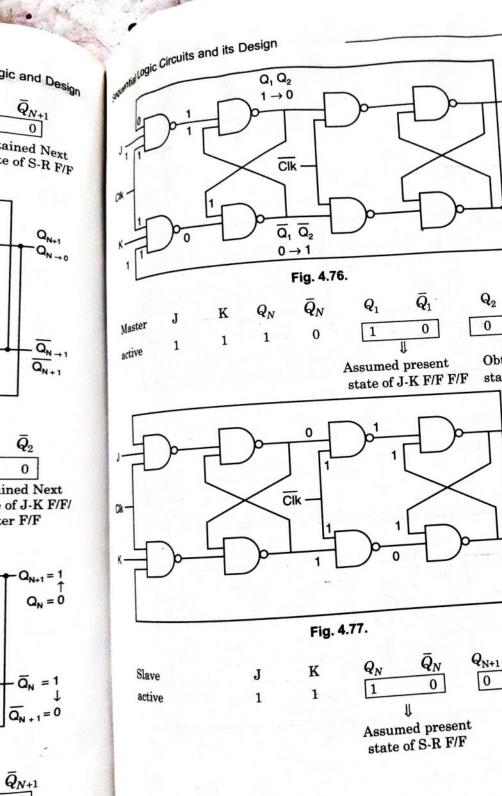

|                      | J K                                | Q,           | ā,            | Q <sub>2</sub>  | $\overline{Q}_2$ | s                 | R              | QN              | Q,         | Q <sub>N+1</sub>  |

|----------------------|------------------------------------|--------------|---------------|-----------------|------------------|-------------------|----------------|-----------------|------------|-------------------|

| CLk                  | 101                                | 0            | 1             | 0               | 1                |                   |                | 0               | 1          | Slave<br>dective  |

| = 1 LG<br>CLk<br>= 0 | -                                  | -Deacti      | e             |                 |                  | 0                 | 1              | 10              | 1          | 1-0               |

| CLk 0                | 0                                  | 1            | 0             | . 1             | 0                |                   | No<br>change ' | 1 1             | 0          | Slave<br>deactive |

| CIL                  | Master                             | Deact condit | ve<br>on of m | aster du        | ring + \         | 1<br>/e Clk pu    | 0<br>use is c  | ` 1<br>opied by | 0<br>slave | -                 |

| CLk 0<br>= 1         | 1                                  | 0            | 1             | 0               | 1                |                   |                | 0               | 1          | Slave decative    |

| = 0                  | Master -                           | Deact        | re            |                 |                  | 0                 | 1              | ,0              | 1          | 10                |

| CLK 0                | 1                                  | .1           | 0             | 0               | 1                | Y-card            | Reset          | 1               | 0          | Slave<br>decative |

| O This copie         | Master -<br>process :<br>d by slav | shown in     | n case        | 2 is knov<br>3k | n as co          | 0<br>cking. Re    | 0<br>eset of m | 1<br>aster du   | ing +ve    |                   |

| 1 1                  | 0                                  | 0            | 1             | 1               | 0                |                   |                | 0               | 1          | Slave<br>deactive |

| ,                    | aster - D                          | eactive      |               |                 | 5                | 1                 | 0              | ,0              | 1          | 1 0               |

|                      | ol otto                            | 1            | 0             | 1.              | 0                |                   | Set (          | 1               | 0          | Slave<br>deactive |

| ) Ivia               | ster - Des<br>process<br>lave duri | shown in     | case 3        | is also co      | cking. Se        | 1<br>t state of r | 0<br>naster du | ring + Ve (     | O -        |                   |

| This                 |                                    | 0            | 1             | 1               | 0                |                   |                | 0               | 1          | Slave<br>deactive |

| This by s            | and the same                       | active       |               |                 |                  | 1                 | 0              | 0               | 1          | 1 0               |

| This by s            | _                                  | -            |               |                 |                  | -                 | . /            | 7               | =          | Slave             |

| This by s            |                                    | ster-Dea     | 0             | 0               | 1                | Togg              | ie (           | 1               | 0          | deactive          |

Action done by master during +Ve CLK is just copied by slave during - VE CLK.

↓ This process is called as

#### Cocking

How Race around condition gets avoided in Master slave J-K Flip Flop

J = K = 1

Similarly

CLK = 1 Then master toggles but slave remains deactive. When CLK = 0 Then slave toggles but master remains deactive. Sequential Logic Circuits & In this way, when

is low for slave F/F, sin effective because CLK ineffective when CLK In this way race a

## 4.16 WHAT IS THE L RACE CONDITI

Generally we take edg or negative edge-

Then if J = K = 1

Now instead of e output keeps on tog oscillations are produ

"Hence if toggl single CLK cycle, generally take CL

## 4.17 APPLICATION

Parallely data of data bits to Application of memory.

Hence we car

- We can divid We can say th Flip-Flop cha direction  $\rightarrow$  1 → For negati

- 1. Flip-Flop Me

- 2. Flip-Flop Me

- 3. Flip-Flop Me

N Flip-Flop Me

Flip-Flops ca

Flip-Flops is

## 4.18 DIFFERENCE

- Latches are

Latches take

- Latches tak

- Latch is sen to glitches.