-ogic and  $D_{e_{Sign}}$

common anode

mentation of

res two 2-bit B > B, A = B

r to realize

uit?

### SEQUENTIAL LOGIC CIRCUITS AND ITS DESIGN

# 4.1. INTRODUCTION

There are two types of Logic Circuits:

- (1) Combinational Logic Circuits

- (2) Sequential Logic Circuits

## (1) Combinational Logic Circuits

In these circuits, output depends only on the present input values.

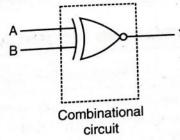

For example: Let us consider an XNOR gate as an combinational circuit.

Fig. 4.1.

The output Y is always depends on the present state of A, B i.e. the present input.

### (2) Sequential Logic Circuits

In these circuits, output can depend on past as well as present input values.

Sequential circuits are the circuit in which memory element is present. Memory element is capable of storing binary digits '0' or '1'.

For example: Let us consider an sequential circuit which is formed by combining memory element and the combinational circuit.

## In This Chapter

#### Inside this Chapter

- Latch

- SR flip flop

- JK flip flop

- Classification of flip flop

- Race around condition

- Master slave JK Flip flop

- D flip flop

- T flip flop

- Conversion of one Flip flop to another

- Counter

- Register

- Shift register

- Universal shift register

- Bidirectional shift register

- Comparison between Latch and flip flop

- Comparison between Ring and Johnson counter

- Designing of sequential circuits

- Excitation table

- Designing of Modulus counter

- **Designing of Asynchronous** (Ripple) counter

faster than sequential circuit

because these circuts don't

DO YOU KNOW?

Asynchronous sequentia

logic circuits are faster than

synchronous sequential logic

circuits.

238 Combinational circuit Memory element B Fig. 4.2.

The value of Y is depends on the present value of A and past value of A.

Let us assume memory element, B hold the initial value zero ('0'). Now if the value of A is 0 there output become 1 and then the value of A is changed to 1 then output is 1. Hence

the value of output Y is depends on present and past value of input A.

Sequential Logic Circuits are of two types:

(1) Synchronous/clocked sequential logic circuits.

(2) Asynchronous/unclocked sequential logic circuits.

#### (1) Synchronous/Clocked Sequential Logic Circuits

In these circuits, event occurs in synchronization with clock pulse. As event is allowed to occur only with synchronization with clock pulse, hence this makes system very much stable, as demanded by latest technology.

#### (2) Asynchronous Sequential Logic Circuits

In these circuits, event occurs without any synchronization with clock pulse. Any event can occur just after combination of another event and hence it does not wait for clock pulse. This makes system unstable.

## 4.2 COMPARISON BETWEEN COMBINATIONAL AND SEQUENTIAL CIRCUITS

#### **Combinational Circuits** Sequential Circuits (1) In these circuits output depends (1) Output can depend on past as well only on the present input values. as present input values. (2) They do not have memory. (2) They do have memory. (3) No feedback is present (3) Feedbacks are present. (4) It is specified by a set of Boolean (4) The outputs are a function of the function. current inputs and the state of (5) It is represented as memory elements (past inputs) (5) It is represented as Combinational Input Combinational Circuit Z Circuit Output Memory (6) They are faster than sequential Z<sub>n</sub> (6) They are not fast due to feedback (7) Examples of combinational action. circuits are Address, Multiple-(7) Examples of sequential circuits are: xers, Subtractors etc. Flip-flops, Counters, Registers etc.

Sequential Logic C Digital Logic and 4.3 LATCH DO YOU KNOW ? Combinational circuits

Latch is a bista 1 or 0 with the associated with can be locked by Hence it is call Latch is also

store one bit o We can ma below:

> In this of  $Q_2$  drive input of Q

$Q_1$  an manufacti

Let's t

Case  $Q_9$ . Becau output of current t and outp

Case output of V<sub>cc</sub>. Thi way Q2

approxi Con

The

Cas Cas ital Logic and Design

DU KNOW ?

onal circuits are sequential circuits ese circuts don't

J KNOW ?

us sequential are faster than sequential logic

below:

nput A.

pulse. As event nce this makes

th clock pulse. hence it does

**AL CIRCUITS**

rcuits

oast as well

on of the tate of nputs)

eedback

cuits are: sters etc.

Sequential Logic Circuits and its Design

4.3 LAND Latch is a bistable device. Bistable device means it can attain two states either latch is a bistable device arrangement Latch 18 at the help of feedback arrangement 1 or 0 with the help of seedback arrangement 10r 0 with it. As one bit of information associated with its bistable sequential associated with this bistable sequential device. Hence it is called as latch. In technical terms, Hence is also known as memory element to store one bit of information - either 1 or 0.

feedback of Because arrangement, latch is also called as sequential circuit.

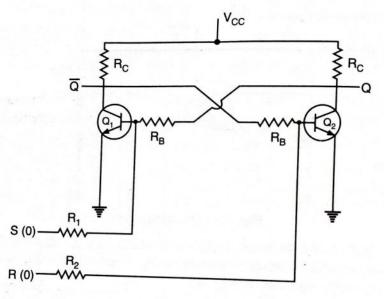

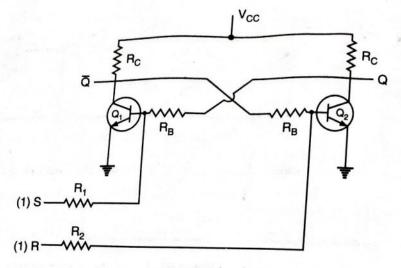

We can make circuit of Latch by using two cross coupled transistors as shown

RC

Fig. 4.3. Transistor Latch

In this diagram, we have two cross coupled transistors  $Q_1$  and  $Q_2$ . The output of  $Q_2$  drives input of  $Q_1$  through resistance  $R_B$ . Similarly the output of  $Q_1$  drives input of  $Q_2$  through resistance  $R_B$ .

$Q_1$  and  $Q_2$  are taken as two similar transistors in terms of their manufacturing, operation and characteristics.

Let's take two cases to explain operation of Transistor Latch:

Case 1: If  $Q_1$  is saturated, then  $V_{CE} = 0$ , means no base current for transistor  $Q_2$  Because output of  $Q_1$  is driving  $Q_2$ . Hence  $Q_2$  goes to cut off state. Hence output of  $Q_2 = V_{CC}$ . This high voltage at output of  $Q_2$  produces enough base current to drive input of  $Q_1$ . In this way  $Q_1$  is sustained in its saturation state and output Q for the overall circuit is approximated as  $V_{\mathrm{CC}}$ .

Case 2: If  $Q_2$  is saturated, then no base current for transistor  $Q_1$ . Because output of  $Q_2$  is driving  $Q_1$ . Hence  $Q_1$  goes to cut off state. Hence output of  $Q_1$  =  $V_{CC}$  This high  $V_{CC}$  produces enough base current to drive input of  $Q_2$ . In this way  $Q_2$  is sustained to work in saturation and output of overall circuit is Q is approximately equal to 0 V.

Concluding case 1 and case 2.

The overall circuit is said to be latched.

Case 1 Summary — "Circuit is latched and storing logic 1."

Case 2 Summary — "Circuit is latched and storing logic 0."

Limitation of Above Circuit State of Above Ci This circuit is not suitable for getting automatically switches to one of the two stable is switched on, then this circuit automatically switches to one of the two stable. states either 1 or 0 and that state is unpredictable.

tes either 1 or 0 and that the transistor late. To avoid above limitation, we can switch over to controlled transistor late.

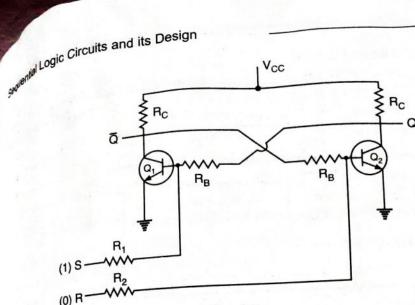

### 4.3.1. Controlled Transistor Latch

If we take two inputs to simple transistor latch. Then we can control this latch. These control inputs can be assigned any value either 1 or 0. The circuit diagram for controlled transistor latch is shown below:

Fig. 4.4.

Case 1:

R = 0

S = 0

Let's assume

Q = 1

As Q = 1, Hence Q is coupled back to input of  $Q_1$ . It means  $Q_1 - ON$ . The output of  $Q_1 = 0$  is coupled to input of  $Q_2$ . In this way  $Q_2$  will be OFF and hence

In this way Q = 1, means no change in output. Output is same as that we have assumed.

Case 2:

R = 0

S = 0

Let's assume Q = 1

Sequential Logic Circu

(1) S

(0) F

High S forces output of overal latched and logic

Case 3:

Let's assum

$\operatorname{High} R$  fo of overall circ logic 0 is stor

Case 4:

Let's ass

tal Logic and D<sub>esign</sub>

tion. When power of the two stable

transistor latch.

can control this or 0. The circuit

-Q

$Q_1$  – ON. The

FF and hence

me as that we

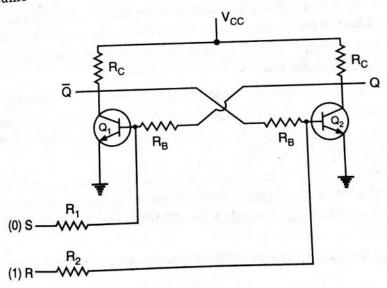

Fig. 4.5.

High S forces the transistor  $Q_1$  to saturate. If  $Q_1$  is in saturation state, then High Stored the High Stored as logic 1. It means circuit is said to be latched and logic 1 is stored.

R = 1Case 3: S = 0Q = 1Let's assume

Fig. 4.6.

High R forces the transistor  $Q_2$  to saturate. If  $Q_2$  is in saturation, then output of overall circuit is obtained as logic 0. It means circuit is said to be latched and logic 0 is stored.

Case 4:

R = 1

S = 1

Let's assume

Q = 1

Fig. 4.7.

If R = S = 1, then  $Q_1$  and  $Q_2$  transistors are forced to saturation.

Suddenly if R and S are returned to low, then both transistors try to comeout of saturation. It will depends on saturation delay time of  $Q_1$  and  $Q_2$  to  $_{\mathtt{COMe}}$ out of saturation. Let's take two cases:

Case 1: If  $Q_1$  is having shorter saturation delay time, then  $Q_1$  is considered as faster transistor than  $oldsymbol{Q}_2$  and hence  $oldsymbol{Q}_1$  will win the race and first come out of saturation. Then overall circuit is said to be latched and overall output Q of

Case 2: If  $Q_2$  is having shorter saturation delay time, then  $Q_2$  is considered as faster transistor than  $Q_1$  and hence  $Q_2$  will win the race and first come out of saturation. Then again overall circuit is said to be latched and overall output  $\varrho$

But we have assumed two similar transistors means  $Q_1$  and  $Q_2$  are equally considered as fast. Now Qoutput of overall circuit is considered as unpredictable. This state is also called as forbidden or invalid state and generally avoided in

Concluding overall analysis with the help of Truth Table as:

| R         | S | To Huth Tab |

|-----------|---|-------------|

| 0         |   | Q           |

| 0         | 0 | No change   |

| 1         | 0 | Set (1)     |

| 1         | 1 | Reset (0)   |

| atch circ | 1 | Race (*)    |

We can construct Latch circuit by using cross coupled NOT Gates, NAND Gates or NOR Gates.

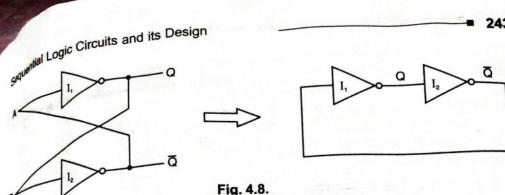

Let's make circuit of a basic latch by using two cross coupled NOT Gates (Inverters):

Sequential Lo

The out  $\overline{Q}$  of inver most comm Case 1

Now Q So we get i

> Case 2 Now Q

So we get

We for

then  $\overline{Q} =$ Limitatio

This ci circuit is stable stat

Remedy

We mo replacing t (two-input

4.4 S-R N

Fig.

gital Logic and D<sub>esign</sub>

ration.

stors try to come  $_1$  and  $Q_2$  to come

$Q_1$  is considered first come out of rall output Q of

$Q_{\scriptscriptstyle 2}$  is considered irst come out of verall output Q

$Q_2$  are equally unpredictable. ally avoided in

Gates, NAND d NOT Gates

The output Q of inverter  $I_1$  is connected as input B of inverter  $I_2$  and output Q of inverter  $I_2$  is coupled as input A of inverter  $I_1$ . This type of connection is most commonly known as cross coupling.

Case 1: Let's take Q = 1

Now Q = B = 1 means input of  $I_2 = 1$ . Hence output of inverter  $I_2$  i.e.,  $\overline{Q} = 0$ . So we get input of inverter  $I_1$  i.e., A = 0. Hence output of inverter  $I_1$  i.e., Q = 1

$$A = 0, \quad B = 1, \quad Q = 1, \quad \overline{Q} = 0$$

Case 2: Let's take Q = 0

Now Q = B = 0 means input of  $I_2 = 0$ . Hence output of inverter  $I_2$  i.e.,  $\overline{Q} = 1$ . So we get input of inverter  $I_1$  i.e., A=1. Hence output of inverter  $I_1$  i.e., Q=0

$$A=1, \quad B=0, \quad Q=0, \quad \overline{Q}=1$$

We found that Q and  $\overline{Q}$  are complementing of each other: means if Q = 1, then  $\overline{Q} = 0$  and else Q = 0, then  $\overline{Q} = 1$ .

Limitation of Logic Circuit

This circuit is not suitable for getting desired digital information when this circuit is switched on, then circuit automatically switches to one of the two stable states, either 1 or 0 and that state is unpredictable.

Remedy to Remove above Limitation

We modify this latch with provision to enter desired digital information by replacing two cross coupled inverters with either two cross coupled NAND gates (two-input) or two cross coupled NOR gates (two-input).

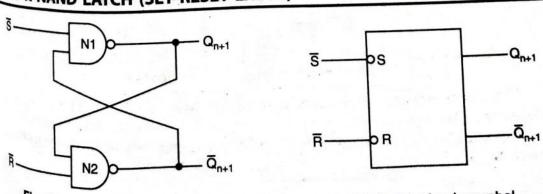

### 44 S-R NAND LATCH (SET-RESET LATCH)

Fig. 4.9. S-R Latch : Circuit Diagram.

Fig. 4.10. S-R Latch : Logic symbol