$$B = \overline{X} Y + Z \overline{(X \oplus Y)} = \overline{X} (X + Y) + \overline{(X \oplus Y)} \overline{(X \oplus Y)} + Z$$

$$= \overline{X + (X + Y)} + \overline{(X \oplus Y)} + \overline{X} \overline{\oplus Y} + Z$$

$$Z$$

Fig. 3.41. Logic diagram of a full subtractor using NOR gates.

### 3.15 PARALLEL BINARY ADDERS

A full adder is capable of adding two 1-bits binary numbers and a carry-in. When two n-bit binary numbers are to be added, the number of full-adders will be equal to the number of bit n in each number. The addition of LSBs can be done by using either a half adder or a full adder with  $C_{in}$  terminal grounded. The carry-out of each full adder is connected to the carry-in of the next higher order adder. A parallel adder is used to add two numbers in parallel form and to produce the sum-bits as parallel outputs. A block diagram of 4-bit parallel adder capable of adding two 4-bit number i.e.  $A_3$   $A_2$   $A_1$   $A_0$  and  $B_3$   $B_2$   $B_1$   $B_0$  is shown in figure 3.39 and resulting outputs sum bits are  $S_3$   $S_2$   $S_1$   $S_0$  and  $C_{out}$  as carry bit e.g. if  $A_3$   $A_2$   $A_1$   $A_0$  1101 and  $B_3$   $B_2$   $B_1$   $B_0$  = 0101.

Therefore, we can see that  $S_3$   $S_2$   $S_1$   $S_0$  = 0010, since the carry-out from the most significant stage is as 1, we have an overflow, *i.e.* the sum (10010) must be expressed in 5-bits.

Fig. 3.42. A 4-bit parallel binary adder.

Parallel outputs

### 3.16 ENCODERS

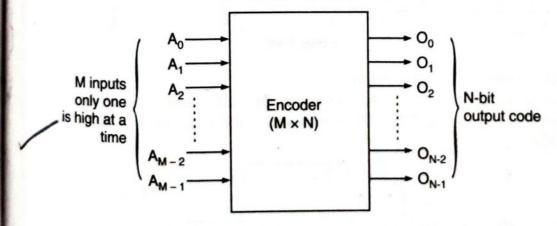

An encoder is considered to be circuit which has multiple inputs and generates particular address at its output. An encoder has a number of input lines, only one of which is activated at a given time and produces an N-bit output code depending on which input is activated.

In Encoder the inputs are decimal digits and/or alphabetic characters and whose outputs are the coded representation of those inputs Encoders performs the operation of encoding which is a process of converting numbers or symbols into a coded format. A block diagram of an encoder with *M* inputs and *N* outputs is shown in figure 3.43.

Fig. 3.43.

Types of encoders are:

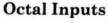

# (1) Octal-to-Binary Encoder

An octal to binary encoder (8 line to 3 line encoder) accepts 8 inputs lines and produces a 3-bit output code corresponding to the activated input. The eight inputs are 0, 1, 2, 3, 4, 5, 6, 7. The truth table is given as follows:

|    | 36.00 |    | Inn | ut (Oct | al)   |       |       | Out | out (Bin |

|----|-------|----|-----|---------|-------|-------|-------|-----|----------|

| Io | $I_1$ | I. | I.  | I,      | $I_5$ | $I_6$ | $I_7$ | A   | В        |

| 1  | 0     | 0  | 0   | 0       | 0     | 0     | 0     | 0   | 0        |

| 0  | 1     | 0  | 0   | 0       | 0     | O     | O     | 0   | . 0      |

| 0  | Ô     | 1  | 0   | 0       | 0     | 0     | O     | 0   | 1        |

| 0  | 0     | Ô  | 1   | 0       | 0     | 0     | 0     | 0   | 1        |

| 0  | ő     | 0  | Ô   | 1       | 0     | 0     | 0     | 1   | 0        |

| 0  | 0     | 0  | 0   | Ô       | 1     | 0     | 0     | 1   | 0        |

| 0  | 0     | 0  | 0   | o       | 0     | 1     | 0     | 1   | 1        |

| 0  | 0     | 0  | 0   | 0       | 0     | Ô     | 1     | 1   | 1        |

The reduced expression for A, B and C is given as

$$A = I_4 + I_5 + I_6 + I_7 \quad B = I_2 + I_3 + I_6 + I_7 \quad C = I_1 + I_3 + I_5 + I_7$$

The realization of the Boolean expression is given as follows:

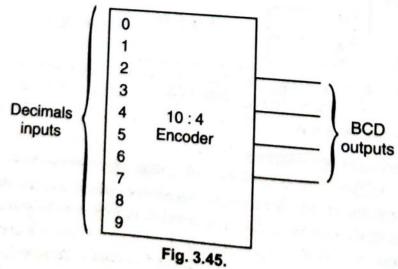

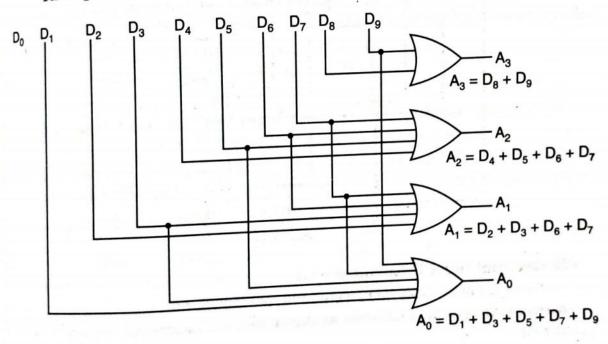

## (2) Decimal to BCD Encoder

This type of encoder has 10 inputs—one for each decimal digit and 4 outputs. Corresponding to the BCD code as shown in block diagram. It is 10 line to 4 line

Combinational Logic Circuits and its Design The truth table is represented as follows:

| Decimal Inputs     | Binary Outputs |       |       |       |  |  |

|--------------------|----------------|-------|-------|-------|--|--|

| Decimal Input      | $A_3$          | $A_2$ | $A_1$ | $A_0$ |  |  |

| 0                  | 0              | 0     | 0     | 0     |  |  |

| $\overline{D_0}$ 1 | 0              | 0     | 0     | 1     |  |  |

| $D_1$ 2            | 0              | 0     | 1     | 0     |  |  |

| $D_2$ 3            | 0              | 0     | 1     | 1     |  |  |

| $D_3$              | 0              | 1     | 0     | 0     |  |  |

| $D_4$ 5            | 0              | 1     | 0     | 1     |  |  |

| $D_5$ 6            | 0              | 1     | 1     | 0     |  |  |

| $D_6$              | 0              | 1     | 1     | 1     |  |  |

| $D_7$ 8            | 1              | 0     | 0     | 0     |  |  |

| $D_8$ 8 9          | 1              | 0     | 0     | 1     |  |  |

The logic diagram is given below:

Fig. 3.46.

#### Code Converters

A type of combinational circuits that convert one code to another code. Main purpose of code converters is to encode the information in such a way that other person is enable to decode your private/secret information.

Hence, code converters more specifically encoders and decoders are used to protect private information benefits of using code converters.

1. Encryption of data more precisely called as cryptography so that private information can be protected. e.g. When we speak into cell phone, an encoder converts the sound of your voice into electrical signal which can travel very fast over very long distances. When the electrical signal reach receivers cell phone, a decoder converts that electrical signal back to sound of your voice. in this way transmitted information remains recure.

2. Code converters are also used to enhance data portablity and tractability.

Enhanced portability means information can be easily transported from one end to another end.

Enhanced tractability means information can be easily stored as well as managed.

- 3. We can also do hardware reduction after doing the code conversion.

- 4. We can also enhance speed of operation and decrease power dissipation. Lets take one example to illustrate this:

Lets take the example of a counter which counts in binary and take the situation of a 4 bit binary counter. When it counters 8 after 7 i.e., transition from 0111 to 1000. All the 4 switches (Flip-flops) takes transition and change their status.

Lets assume that taking transition from  $1 \to 0$  indicates switch off and taking transition from  $0 \to 1$  indicates switch on.

It indicates switching activity is very high. As we know that high switching activity, lead to low speed of operation and very high power dissipation.

Now if we use a code converters and uv gray coding, then biggest advantage of gray code isthat, only 1 bit changes between 2 consecutive numbers. e..g.,

we see that here only one switch takes a transition from 0 to 1 and rest of 3 switches wants change. Hence, switching activity is less.

In this way speed of operation becomes high and power dissipation becomes low.

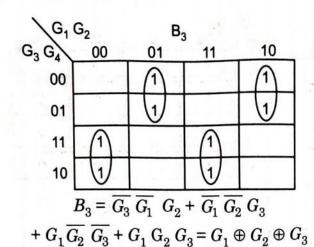

# (1) Gray to Binary code converter

To design a circuit for Gray to binary code converter we proceed as follows:

The conversion table for binary to Gray Code is written first and then interchange the inputs means Gray is input and output is binary code. In this  $B_2$ ,  $B_3$ ,  $B_4$  as the output bits.

Combinational Logic Circuits and its Design ofor Gray to Binary Code is given as follows:

| Truth to | able for Gra |       | Gray  | Codes |       |       | 1                    | Bina  | ry    |       |

|----------|--------------|-------|-------|-------|-------|-------|----------------------|-------|-------|-------|

| Truth to | Vumber       | $G_1$ | $G_2$ | $G_3$ | $G_4$ |       | $\boldsymbol{B}_{I}$ | $B_2$ | $B_3$ | $B_4$ |

| _        |              | 0     | 0     | 0     | . 0   |       | 0                    | 0     | 0     | 0     |

| 0        |              | 0     | 0     | 0     | 1     |       | 0                    | 0     | 0     | 1     |

| 1        |              | 0     | 0     | 1     | 1     |       | 0                    | 0     | 1     | 0     |

| 2        |              | 0     | 0     | 1     | 0     |       | 0                    | 0     | 1     | 1     |

| 3        |              | 0     | 1     | 1     | 0     |       | 0                    | 1     | 0     | 0     |

| 4        |              | 0     | 1     | 1     | 1.    |       | 0                    | 1 .   | 0     | 1     |

| 5        |              | 0     | 1     | 0     | 1     |       | 0                    | 1 ·   | 1     | 0     |

| 6        |              | 0 .   | 1     | 0     | 07    |       | 0                    | 1,    | 1     | 17    |

| 7        |              | 1     | 1     | 0     | 08    |       | 1                    | O     | 0     | 08    |

| 8        |              | 1     | 1     | 0     | 1     | 16.12 | 1                    | 0     | 0     | 1     |

| 9        |              | 1     | 1     | 1.    | 1     |       | 1                    | 0     | 1     | 0     |

| 10       |              | 1.    | 1     | 1     | 0     |       | 1                    | 0     | ĺ     | 1     |

| 11       |              | 1     | 0     | 1     | 0     |       | 1                    | 1     | 0     | 0     |

| 12       |              | 1     | 0     | 1     | 1     |       | 1                    | 1     | 0     | 1     |

| 13       |              | 1     | 0     | 0     | 1     |       | 1                    | 1     | 1     | Ô     |

| 14       |              | 1     | 0     | 0     | 1     |       | 1                    | 1     | 1     | 1     |

| 14<br>15 | V/Vr         | 1     | 0     | 0     | 0     |       | 1                    | 1     | ,1    |       |

The output  $B_1$ ,  $B_2$ ,  $B_3$  and  $B_4$  can be expressed as interms of minterms are as follows:

$$B_1 = \Sigma m \ (8, 9, 10, 11, 12, 13, 14, 15)$$

$B_2 = \Sigma m \ (4, 5, 6, 7, 8, 9, 10, 11)$

$$B_3 = \Sigma m \ (2, 3, \frac{4.5}{5}, \frac{8.9}{10.11}, \frac{14.15}{10.11})$$

$B_4 = \Sigma m \ (\frac{1.2.4.7.8.11.13.14}{13.5.7.9.11.13.15}$

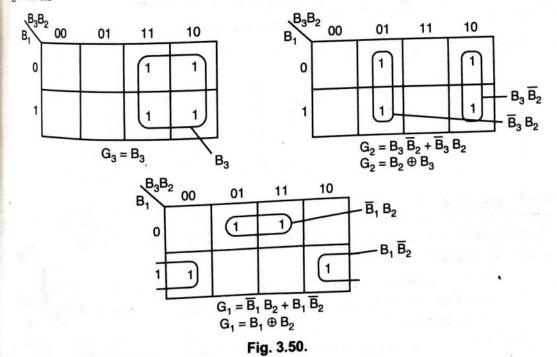

The K-maps for these variables are as follows:

| \G <sub>1</sub> | $G_2$            | В   | 1   |     | G         | G <sub>2</sub> | $B_4$ |     |     |

|-----------------|------------------|-----|-----|-----|-----------|----------------|-------|-----|-----|

| $G_3 G_4$       | 00               | 01  | 11  | 10  | $G_3 G_4$ | 00             | 01    | 11  | 10  |

| 00              | 0                | 4   | 1,- | 18  | 00        | 0              | 1,    | 12  | 15  |

| 01              | 1                | 5   | 1,  | 19  | 01        | 1,             | 5     | 1,2 | 9   |

| 11              | . 2              | 6   | 1 1 | 1 1 | 11        | 3              | 1,    | 15  | 1,, |

| 10              | , (              | , 2 | 1.  | 1   | 10        | 12             | 6     | 1,4 | ل ا |

| $B_1 =$         | $\overline{G_1}$ |     |     |     |           |                |       |     |     |

$$B_{4} = \bar{G}_{1}G_{2} \ \bar{G}_{3}\bar{G}_{4} + G_{1}\bar{G}_{2}\bar{G}_{3}\bar{G}_{4} + \bar{G}_{1}\bar{G}_{2} \ \bar{G}_{3} \ G_{4} + G_{1}G_{2}\bar{G}_{3}G_{4} \\ + \bar{G}_{1}G_{2}G_{3}G_{4} + G_{1}\bar{G}_{2}G_{3}G_{4} + \bar{G}_{1}\bar{G}_{2}G_{3}\bar{G}_{4} + G_{1}G_{2}G_{3}\bar{G}_{4} \\ \Rightarrow \ \bar{G}_{1}G_{2}\bar{G}_{3}\bar{G}_{4} + \bar{G}_{1}\bar{G}_{2}\bar{G}_{3}G_{4} + G_{1}\bar{G}_{2}\bar{G}_{3}\bar{G}_{4} + G_{1}G_{2}\bar{G}_{3}G_{4} \\ \Rightarrow \ \bar{G}_{1}G_{2}\bar{G}_{3}\bar{G}_{4} + \bar{G}_{1}\bar{G}_{2}G_{3}G_{4} + \bar{G}_{1}\bar{G}_{2}G_{3}G_{4} + G_{1}G_{2}G_{3}\bar{G}_{4} \\ \Rightarrow \ \bar{G}_{1}\bar{G}_{3}[G_{2}\bar{G}_{4} + \bar{G}_{2}G_{4}] + G_{1}\bar{G}_{3}[\bar{G}_{2}G_{4} + G_{2}G_{4}] + \bar{G}_{1}G_{3}\\ \bar{G}_{2}G_{4} + \bar{G}_{2}\bar{G}_{4}] + G_{1}G_{3}[\bar{G}_{2}G_{4} + G_{2}\bar{G}_{4}] \\ \Rightarrow \ \bar{G}_{1}\bar{G}_{3}[G_{2}\oplus G_{4}] + G_{1}\bar{G}_{3}[G_{2}\oplus G_{4}] + G_{1}G_{3}[G_{2}\oplus G_{4}] + \bar{G}_{1}G_{3}[G_{2}\oplus G_{4}] \\ \Rightarrow \ \bar{G}_{1}\bar{G}_{3}[G_{2}\oplus G_{4}] + G_{1}G_{3}[G_{2}\oplus G_{4}] + G_{1}\bar{G}_{3}[G_{2}\oplus G_{4}] \\ \Rightarrow \ \bar{G}_{1}\bar{G}_{3}[G_{2}\oplus G_{4}] + G_{1}G_{3}[G_{2}\oplus G_{4}] + G_{1}\bar{G}_{3}[G_{2}\oplus G_{4}] \\ \Rightarrow \ \bar{G}_{1}\bar{G}_{3}[G_{2}\oplus G_{4}] + G_{1}G_{3}[G_{2}\oplus G_{4}] + G_{1}\bar{G}_{3}[G_{2}\oplus G_{4}] \\ \Rightarrow \ \bar{G}_{1}\bar{G}_{3}[G_{2}\oplus G_{4}] + G_{1}G_{3}[G_{2}\oplus G_{4}] + G_{1}G_{3}[G_{2}\oplus G_{4}] \\ \Rightarrow \ \bar{G}_{1}\bar{G}_{3}[G_{2}\oplus G_{4}] + G_{1}G_{3}[G_{2}\oplus G_{4}] + G_{1}G_{3}[G_{2}\oplus G_{4}] \\ \Rightarrow \ \bar{G}_{1}\bar{G}_{3}[G_{2}\oplus G_{4}] + G_{1}G_{3}[G_{2}\oplus G_{4}] + G_{1}G_{3}[G_{2}\oplus G_{4}] \\ \Rightarrow \ \bar{G}_{1}\bar{G}_{3}[G_{2}\oplus G_{4}] + G_{1}G_{3}[G_{2}\oplus G_{4}] + G_{1}G_{3}[G_{2}\oplus G_{4}] \\ \Rightarrow \ \bar{G}_{1}\bar{G}_{3}[G_{2}\oplus G_{4}] + G_{1}G_{3}[G_{2}\oplus G_{4}] + G_{1}G_{3}[G_{2}\oplus G_{4}] \\ \Rightarrow \ \bar{G}_{1}\bar{G}_{3}[G_{2}\oplus G_{4}] + G_{1}G_{3}[G_{2}\oplus G_{4}] + G_{1}G_{3}[G_{2}\oplus G_{4}] \\ \Rightarrow \ \bar{G}_{1}\bar{G}_{3}[G_{2}\oplus G_{4}] + G_{1}G_{3}[G_{2}\oplus G_{4}] + G_{1}G_{3}[G_{2}\oplus G_{4}] \\ \Rightarrow \ \bar{G}_{1}\bar{G}_{2}[G_{2}\oplus G_{4}] + G_{1}G_{2}[G_{2}\oplus G_{4}] + G_{1}G_{3}[G_{2}\oplus G_{4}] \\ \Rightarrow \ \bar{G}_{1}\bar{G}_{2}[G_{2}\oplus G_{4}] + G_{1}G_{2}[G_{2}\oplus G_{4}] + G_{1}G_{2}[G_{2}\oplus G_{4}] \\ \Rightarrow \ \bar{G}_{1}\bar{G}_{2}[G_{2}\oplus G_{4}] + G_{1}G_{2}[G_{2}\oplus G_{4}] + G_{1}G_{2}[G_{2}\oplus G_{4}] \\ \Rightarrow \ \bar{G}_{2}[G_{2}\oplus G_{4}] + G_{2}[G_{$$

$$\begin{split} & \Rightarrow \qquad [\bar{G}_1\bar{G}_3 + G_1G_3] \, [G_2 \oplus G_4] + [G_1\bar{G}_3 + \bar{G}_1G_3] \, [G_2 \odot G_4] \\ & = \, [G_1 \odot G_3] \, [G_2 \oplus G_4] + [G_1 \oplus G_3] \, [G_2 \odot G_4] \\ & = \, G_1 \oplus G_2 \oplus G_3 \oplus G_4 \end{split}$$

| \ G1 (                        | $\Theta_2$         |    | $B_2$   |                      | all              |

|-------------------------------|--------------------|----|---------|----------------------|------------------|

| G <sub>3</sub> G <sub>4</sub> | 00                 | 0  | 1       | 11                   | 10               |

| 00                            | 0                  | 1  | 4       | 12                   | 1                |

| 01                            | . , 1              | 1  | 5       | 13                   | 110              |

| 11                            | 3                  | 1  | 7       | 15                   |                  |

| 10                            | 2                  | 1  | 6       | 14                   | 110              |

|                               | $=\overline{G_1}G$ | 2+ | $G_1$ · | $\overline{G_2} = C$ | $G_1 \oplus G_2$ |

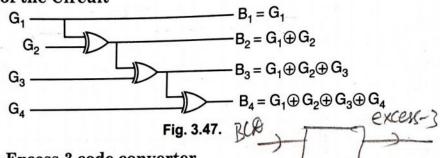

Designing of the Circuit

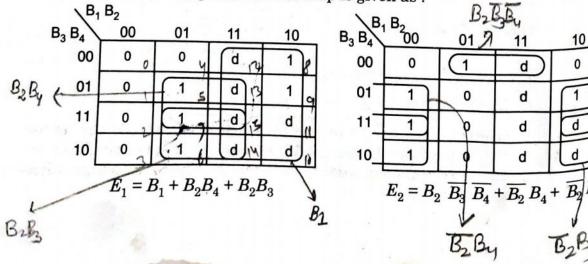

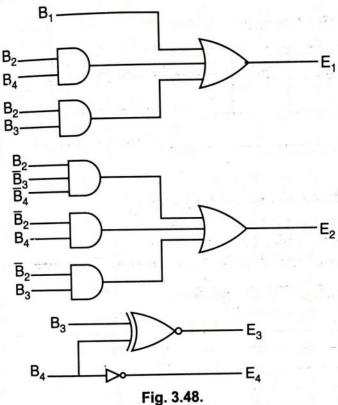

(2) BCD to Excess-3 code converter

In order to convert the BCD to Excess-3, we first write down the truth table of BCD to excess-3 code. The corresponding to decimal numbers 10, 11, 12, 13, 14 and 15 are considered as don't care terms. The truth table is as follows:

| Decimal | Number |                    | BCD   | Codes |       |   | Exc                | ess-3 | Cod   | e     |

|---------|--------|--------------------|-------|-------|-------|---|--------------------|-------|-------|-------|

|         |        | $\boldsymbol{B}_1$ | $B_2$ | $B_3$ | $B_4$ |   | $\boldsymbol{E_1}$ | $E_2$ | $E_3$ | $E_4$ |

| 0       |        | 0                  | 0     | 0     | 0     |   | 0                  | 0     | 1     | 1     |

| 1       |        | 0                  | 0     | 0     | 1     |   | 0                  | - 1   | 0     | 0     |

| 2       | -      | 0                  | 0     | 1     | 0     |   | 0                  | 1     | 0     | 1     |

| 3       |        | 0                  | 0     | 1     | 1     |   | 0                  | 1     | 1     | 0     |

| 4       |        | 0                  | 1     | 0     | 0     | - | 0                  | 1     | 1     | 1     |

| 5       | -      | 0                  | 1     | 0     | 1     |   | 1.                 | 0     | 0     | 0     |

| 6       | -      | 0                  | 1     | 1     | 0     |   | 1                  | 0     | 0     | 1     |

| 7       |        | 0                  | 1     | 1     | 1     |   | 1                  | 0     | 1     | 0     |

| 8       |        | 1                  | 0     | 0     | 0     |   | 1                  | 0     | 1     | 1     |

| 9       |        | 1                  | 0     | 0     | 1     |   | 1                  | 1     | 0     | 0     |

The reduced expression for K-map is given as:

| 1 | ď | 1     |

|---|---|-------|

|   |   |       |

| 0 | d | 0     |

| 0 | d | d     |

| 1 | d | . , d |

|   | 0 | 0 d   |

01

11

$E_4 = \overline{B_4}$

$\underbrace{E_3 = \widehat{B_3} \ \widehat{B_4} + B_3 B_4}_{\text{The circuit realization is given as follows:}}_{B_3 \oplus B_4}$

d

d

d

0

d

d

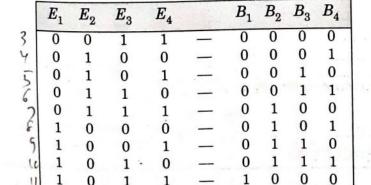

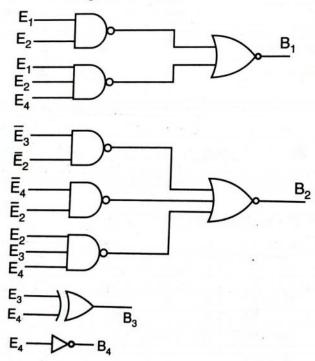

#### (3) Excess-3 to BCD code converter

Truth table is as follows:

0

0

In this encoder Excess-3 is input and BCD code is output. As the terms Orresponding to decimal number 0, 1, 2, 13, 14, 15 will not appear in Excess-3 ode the code the code and expression code, these terms are considered as don't care terms (d). The Boolean expression is given as after solving K-maps are :-

0

0

| \                             | _                                |           |                |       |                                           | =1 E <sub>2</sub>         | 01      | 11      | 10 |

|-------------------------------|----------------------------------|-----------|----------------|-------|-------------------------------------------|---------------------------|---------|---------|----|

| E3 E4                         | E <sub>2</sub> 00                | 01        | 11             | 10    | E <sub>3</sub> E <sub>4</sub> 00          | H                         | 1       | 1       |    |

| 00                            | d <sub>o</sub>                   | 0 4       | $\binom{1}{n}$ | 8 0   | 01                                        | -1                        | 0       | d       | 0  |

| 01                            | dι                               | 0 5       | d B            | 09    | 11                                        | -                         | 0       | d       | 0  |

| 11                            | 0 3                              | 0 7       | 0 19           | 1),,  | 10                                        |                           | 1       | d       |    |

| 10                            | d 2                              | 0 6       | a 14           | 0 0   |                                           | 4                         |         |         | 4  |

|                               | $B_1$ =                          | $=E_1E_2$ | $+E_1E_3$      | $E_4$ |                                           |                           | $B_4 =$ | $E_4$   |    |

|                               |                                  |           |                |       |                                           |                           |         |         |    |

| E E                           | E <sub>1</sub> E <sub>2</sub> 00 | 01        | 11             | 10    | E E                                       | E <sub>2</sub> 00         | 01      | 11      | 10 |

| E <sub>3</sub> E <sub>4</sub> | 1 E <sub>200</sub>               | 01        | 11             |       | E <sub>3</sub> E <sub>4</sub>             | E <sub>2</sub><br>00<br>d | 01      | 11<br>0 | 10 |

| 0 4                           | _                                |           |                |       | E <sub>3</sub> E <sub>4</sub>             | 00                        |         |         |    |

| 00                            |                                  | 0 ,       | 0              |       | E <sub>3</sub> E <sub>4</sub>             | 00<br>d                   | 0       | 0       |    |

| 00                            | 9                                | 0 ,       | o<br>d         | 10    | E <sub>3</sub> E <sub>4</sub><br>00<br>01 | 00<br>d                   | 1       | 0<br>d  | 0  |

The circuit realization is given as follows:

Fig. 3.49.

#### 3.17 DESIGN PROCEDURE

We can design any combinational circuit by determination of boolean functions. Steps of designing are as follows:

1. Find out the number of inputs and outputs by provided specifications about the combinational circuit. Assign arbitrary variables to all inputs and outputs.

Combinational Logic Circuits and its Design By making the input combinations based on arbitrary input variables, By making make the truth table corresponding to relationship between input we can make the truth table corresponding to relationship between input wariables. and output variables.

Find out the boolean function corresponding to each output variable as Find out variable. K-map approach can be utilized to obtain a function of input variable. K-map approach can be utilized to obtain simplied boolean functions.

4. Based on boolean functions, draw the logic diagram.

5. Verify obtained circuit design manually or by using logic simulation.

Let us explain it with an example. Suppose we want to convert '3' bit binary Let us only code. It requires 3 bits  $B_3$ ,  $B_2$ ,  $B_1$  for input and three bits for output ode to gray code. For '3' bits the combinations of inputs (03 - 0) ode to gray  $G_3$ ,  $G_2$ ,  $G_3$ . For '3' bits the combinations of inputs ( $2^3 = 8$ ) are 000 to 111. Next step is to draw the truth table taking input and output values. It is given

| В | inary coo | le    | G     | Gray code |       |  |  |  |

|---|-----------|-------|-------|-----------|-------|--|--|--|

| B | $B_{2}$   | $B_1$ | $G_3$ | $G_2$     | $G_1$ |  |  |  |

| 0 | 0         | 0     | . 0.  | 0         | 0     |  |  |  |

| 0 | 0         | 1     | 0     | 0         | 1     |  |  |  |

| 0 | 1         | 0     | 0     | 1         | 1     |  |  |  |

| 0 | 1         | 1     | 0     | 1         | 0     |  |  |  |

| 1 | 0         | 0     | 1     | 1         | 0     |  |  |  |

| 1 | 0         | 1     | 1     | 1         | 1     |  |  |  |

| 1 | 1         | 0     | 1     | . 0       | 1     |  |  |  |

| 1 | 1         | 1     | 1     | 0         | . 0   |  |  |  |

Next step is to determine the value of  $G_3$ ,  $G_2$  and  $G_1$ . It is obtained by taking  $B_3$ ,  $B_2$  and  $B_1$  (inputs) and solving the k map corresponding to each outputs  $G_3$ ,  $G_2$  and  $G_1$ . The three inputs are there, so three variable k-map is used. It is given as